#include "plat_i3c.h"

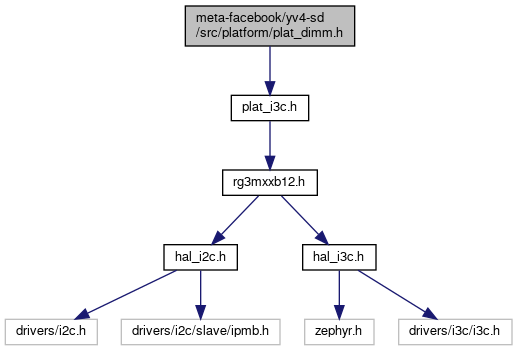

Include dependency graph for plat_dimm.h:

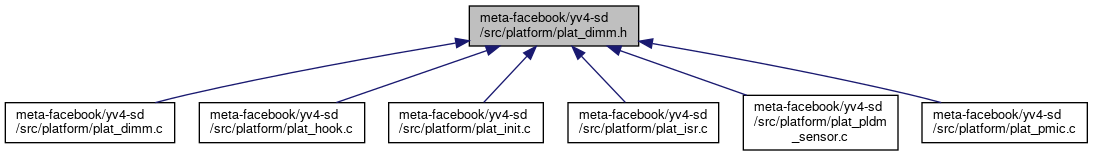

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | dimm_info |

Macros | |

| #define | DIMM_SPD_A_G_ADDR (0xA0 >> 1) |

| #define | DIMM_SPD_B_H_ADDR (0xA2 >> 1) |

| #define | DIMM_SPD_C_I_ADDR (0xA4 >> 1) |

| #define | DIMM_SPD_D_J_ADDR (0xA6 >> 1) |

| #define | DIMM_SPD_E_K_ADDR (0xA8 >> 1) |

| #define | DIMM_SPD_F_L_ADDR (0xAA >> 1) |

| #define | DIMM_PMIC_A_G_ADDR 0x48 |

| #define | DIMM_PMIC_B_H_ADDR 0x49 |

| #define | DIMM_PMIC_C_I_ADDR 0x4A |

| #define | DIMM_PMIC_D_J_ADDR 0x4B |

| #define | DIMM_PMIC_E_K_ADDR 0x4C |

| #define | DIMM_PMIC_F_L_ADDR 0x4D |

| #define | CPLD_ADDR 0x21 |

| #define | MAX_LEN_I3C_GET_PMIC_ERR 47 |

| #define | MAX_LEN_I3C_GET_PMIC_PWR 1 |

| #define | MAX_LEN_I3C_GET_SPD_TEMP 2 |

| #define | DIMM_I3C_MUX_CONTROL_OFFSET 0x0C |

| #define | I3C_MUX_BIC_TO_DIMMA_TO_F 0x02 |

| #define | I3C_MUX_BIC_TO_DIMMG_TO_L 0x03 |

| #define | I3C_MUX_CPU_TO_DIMM 0x00 |

| #define | DIMM_I3C_MUX_STATUS_OFFSET 0x0D |

| #define | I3C_MUX_STATUS_ENABLE_FUNCTION_CHECK 7 |

| #define | I3C_MUX_STATUS_PD_SPD_1_REMOTE_EN 6 |

| #define | I3C_MUX_STATUS_PD_SPD_2_REMOTE_EN 5 |

| #define | I3C_MUX_STATUS_SPD_MASK 0x60 |

| #define | I3C_DIMM_MUTEX_TIMEOUT_MS 1000 |

| #define | GET_DIMM_INFO_TIME_MS 1000 |

| #define | GET_DIMM_INFO_STACK_SIZE 2304 |

| #define | SPD_MFG_START 0x200 |

| #define | SPD_MFG_TOTAL_LEN 128 |

| #define | SPD_TEMP_DATA_LEN 2 |

| #define | PMIC_PWR_DATA_LEN 1 |

| #define | SPD_RAW_LEN 0x50 |

| #define | SPD_TYPE 0x00 /* 0x02 (1) */ |

| #define | SPD_SZ_B4 0x01 /* 0x04 (size_die) (1) */ |

| #define | SPD_SZ_B6 0x02 /* 0x06 (device_width) (1) */ |

| #define | SPD_SPEED_L 0x03 /* 0x14 (1) */ |

| #define | SPD_SPEED_H 0x04 /* 0x15 (1) */ |

| #define | SPD_PMICVEN_L 0x05 /* 0xC6 (1) */ |

| #define | SPD_PMICVEN_H 0x06 /* 0xC7 (1) */ |

| #define | SPD_REGVEN_L 0x07 /* 0xF0 (1) */ |

| #define | SPD_REGVEN_H 0x08 /* 0xF1 (1) */ |

| #define | SPD_SZ_BEA 0x09 /* 0xEA (pkg_rank) (1) */ |

| #define | SPD_SZ_BEB 0x0A /* 0xEB (bus_width/ch) (1) */ |

| #define | SPD_MFG_ID_L 0x0B /* 0x200 (1) */ |

| #define | SPD_MFG_ID_H 0x0C /* 0x201 (1) */ |

| #define | SPD_MFG_LOC 0x0D /* 0x202 (1) */ |

| #define | SPD_MFG_YY 0x0E /* 0x203 (year) (1) */ |

| #define | SPD_MFG_WW 0x0F /* 0x204 (week) (1) */ |

| #define | SPD_SN_OFF 0x10 /* 0x205..0x208 (4) */ |

| #define | SPD_SN_LEN 4 |

| #define | SPD_PN_OFF 0x14 /* 0x209..0x226 (30) */ |

| #define | SPD_PN_LEN 30 |

| #define | SPD_PAYLOAD_LEN (SPD_C_PN_OFF + SPD_C_PN_LEN) /* = 50 bytes */ |

| #define | SPD_OEM_PRESENT 0x4E /* 1 byte: 1=present, 0=not present */ |

| #define | SPD_OEM_STATUS 0x4F /* 1 byte: bit0=SPD compact ready */ |

| #define | SPD_OEM_STATUS_SPD_READY 0x01 |

Typedefs | |

| typedef struct dimm_info | dimm_info |

Functions | |

| void | start_get_dimm_info_thread () |

| void | get_dimm_info_handler () |

| uint8_t | sensor_num_map_dimm_id (uint8_t sensor_num) |

| int | pal_get_spd_temp (uint8_t sensor_num, uint8_t *data) |

| int | pal_get_pmic_pwr (uint8_t sensor_num, uint8_t *data) |

| void | clear_unaccessible_dimm_data (uint8_t dimm_id) |

| int | switch_i3c_dimm_mux (uint8_t i3c_ctrl_mux_data) |

| int | check_i3c_dimm_mux (uint8_t *status_data) |

| int | all_brocast_ccc (I3C_MSG *i3c_msg) |

| int | init_dimm_prsnt_status () |

| uint8_t | get_dimm_present (uint8_t dimm_id) |

| void | set_spd_raw_ready (uint8_t dimm_id, bool ready) |

| bool | get_spd_raw_ready (uint8_t dimm_id) |

| int | plat_get_spd_raw (uint8_t dimm_id, uint8_t **buf_out, bool *ready_out) |

Variables | |

| struct k_mutex | i3c_dimm_mutex |

| uint8_t | spd_i3c_addr_list [] |

| uint8_t | pmic_i3c_addr_list [] |

Macro Definition Documentation

◆ CPLD_ADDR

| #define CPLD_ADDR 0x21 |

◆ DIMM_I3C_MUX_CONTROL_OFFSET

| #define DIMM_I3C_MUX_CONTROL_OFFSET 0x0C |

◆ DIMM_I3C_MUX_STATUS_OFFSET

| #define DIMM_I3C_MUX_STATUS_OFFSET 0x0D |

◆ DIMM_PMIC_A_G_ADDR

| #define DIMM_PMIC_A_G_ADDR 0x48 |

◆ DIMM_PMIC_B_H_ADDR

| #define DIMM_PMIC_B_H_ADDR 0x49 |

◆ DIMM_PMIC_C_I_ADDR

| #define DIMM_PMIC_C_I_ADDR 0x4A |

◆ DIMM_PMIC_D_J_ADDR

| #define DIMM_PMIC_D_J_ADDR 0x4B |

◆ DIMM_PMIC_E_K_ADDR

| #define DIMM_PMIC_E_K_ADDR 0x4C |

◆ DIMM_PMIC_F_L_ADDR

| #define DIMM_PMIC_F_L_ADDR 0x4D |

◆ DIMM_SPD_A_G_ADDR

| #define DIMM_SPD_A_G_ADDR (0xA0 >> 1) |

◆ DIMM_SPD_B_H_ADDR

| #define DIMM_SPD_B_H_ADDR (0xA2 >> 1) |

◆ DIMM_SPD_C_I_ADDR

| #define DIMM_SPD_C_I_ADDR (0xA4 >> 1) |

◆ DIMM_SPD_D_J_ADDR

| #define DIMM_SPD_D_J_ADDR (0xA6 >> 1) |

◆ DIMM_SPD_E_K_ADDR

| #define DIMM_SPD_E_K_ADDR (0xA8 >> 1) |

◆ DIMM_SPD_F_L_ADDR

| #define DIMM_SPD_F_L_ADDR (0xAA >> 1) |

◆ GET_DIMM_INFO_STACK_SIZE

| #define GET_DIMM_INFO_STACK_SIZE 2304 |

◆ GET_DIMM_INFO_TIME_MS

| #define GET_DIMM_INFO_TIME_MS 1000 |

◆ I3C_DIMM_MUTEX_TIMEOUT_MS

| #define I3C_DIMM_MUTEX_TIMEOUT_MS 1000 |

◆ I3C_MUX_BIC_TO_DIMMA_TO_F

| #define I3C_MUX_BIC_TO_DIMMA_TO_F 0x02 |

◆ I3C_MUX_BIC_TO_DIMMG_TO_L

| #define I3C_MUX_BIC_TO_DIMMG_TO_L 0x03 |

◆ I3C_MUX_CPU_TO_DIMM

| #define I3C_MUX_CPU_TO_DIMM 0x00 |

◆ I3C_MUX_STATUS_ENABLE_FUNCTION_CHECK

| #define I3C_MUX_STATUS_ENABLE_FUNCTION_CHECK 7 |

◆ I3C_MUX_STATUS_PD_SPD_1_REMOTE_EN

| #define I3C_MUX_STATUS_PD_SPD_1_REMOTE_EN 6 |

◆ I3C_MUX_STATUS_PD_SPD_2_REMOTE_EN

| #define I3C_MUX_STATUS_PD_SPD_2_REMOTE_EN 5 |

◆ I3C_MUX_STATUS_SPD_MASK

| #define I3C_MUX_STATUS_SPD_MASK 0x60 |

◆ MAX_LEN_I3C_GET_PMIC_ERR

| #define MAX_LEN_I3C_GET_PMIC_ERR 47 |

◆ MAX_LEN_I3C_GET_PMIC_PWR

| #define MAX_LEN_I3C_GET_PMIC_PWR 1 |

◆ MAX_LEN_I3C_GET_SPD_TEMP

| #define MAX_LEN_I3C_GET_SPD_TEMP 2 |

◆ PMIC_PWR_DATA_LEN

| #define PMIC_PWR_DATA_LEN 1 |

◆ SPD_MFG_ID_H

| #define SPD_MFG_ID_H 0x0C /* 0x201 (1) */ |

◆ SPD_MFG_ID_L

| #define SPD_MFG_ID_L 0x0B /* 0x200 (1) */ |

◆ SPD_MFG_LOC

| #define SPD_MFG_LOC 0x0D /* 0x202 (1) */ |

◆ SPD_MFG_START

| #define SPD_MFG_START 0x200 |

◆ SPD_MFG_TOTAL_LEN

| #define SPD_MFG_TOTAL_LEN 128 |

◆ SPD_MFG_WW

| #define SPD_MFG_WW 0x0F /* 0x204 (week) (1) */ |

◆ SPD_MFG_YY

| #define SPD_MFG_YY 0x0E /* 0x203 (year) (1) */ |

◆ SPD_OEM_PRESENT

| #define SPD_OEM_PRESENT 0x4E /* 1 byte: 1=present, 0=not present */ |

◆ SPD_OEM_STATUS

| #define SPD_OEM_STATUS 0x4F /* 1 byte: bit0=SPD compact ready */ |

◆ SPD_OEM_STATUS_SPD_READY

| #define SPD_OEM_STATUS_SPD_READY 0x01 |

◆ SPD_PAYLOAD_LEN

| #define SPD_PAYLOAD_LEN (SPD_C_PN_OFF + SPD_C_PN_LEN) /* = 50 bytes */ |

◆ SPD_PMICVEN_H

| #define SPD_PMICVEN_H 0x06 /* 0xC7 (1) */ |

◆ SPD_PMICVEN_L

| #define SPD_PMICVEN_L 0x05 /* 0xC6 (1) */ |

◆ SPD_PN_LEN

| #define SPD_PN_LEN 30 |

◆ SPD_PN_OFF

| #define SPD_PN_OFF 0x14 /* 0x209..0x226 (30) */ |

◆ SPD_RAW_LEN

| #define SPD_RAW_LEN 0x50 |

◆ SPD_REGVEN_H

| #define SPD_REGVEN_H 0x08 /* 0xF1 (1) */ |

◆ SPD_REGVEN_L

| #define SPD_REGVEN_L 0x07 /* 0xF0 (1) */ |

◆ SPD_SN_LEN

| #define SPD_SN_LEN 4 |

◆ SPD_SN_OFF

| #define SPD_SN_OFF 0x10 /* 0x205..0x208 (4) */ |

◆ SPD_SPEED_H

| #define SPD_SPEED_H 0x04 /* 0x15 (1) */ |

◆ SPD_SPEED_L

| #define SPD_SPEED_L 0x03 /* 0x14 (1) */ |

◆ SPD_SZ_B4

| #define SPD_SZ_B4 0x01 /* 0x04 (size_die) (1) */ |

◆ SPD_SZ_B6

| #define SPD_SZ_B6 0x02 /* 0x06 (device_width) (1) */ |

◆ SPD_SZ_BEA

| #define SPD_SZ_BEA 0x09 /* 0xEA (pkg_rank) (1) */ |

◆ SPD_SZ_BEB

| #define SPD_SZ_BEB 0x0A /* 0xEB (bus_width/ch) (1) */ |

◆ SPD_TEMP_DATA_LEN

| #define SPD_TEMP_DATA_LEN 2 |

◆ SPD_TYPE

| #define SPD_TYPE 0x00 /* 0x02 (1) */ |

Typedef Documentation

◆ dimm_info

Enumeration Type Documentation

◆ DIMM_DEVICE_TYPE

| enum DIMM_DEVICE_TYPE |

◆ DIMM_ID

| enum DIMM_ID |

◆ DIMM_PRSNT_STATUS

| enum DIMM_PRSNT_STATUS |

◆ NUMBER_DIMM_PMIC_PWR

| enum NUMBER_DIMM_PMIC_PWR |

◆ NUMBER_DIMM_TEMP

| enum NUMBER_DIMM_TEMP |

Function Documentation

◆ all_brocast_ccc()

| int all_brocast_ccc | ( | I3C_MSG * | i3c_msg | ) |

Here is the call graph for this function:

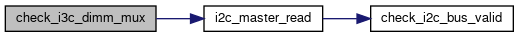

◆ check_i3c_dimm_mux()

| int check_i3c_dimm_mux | ( | uint8_t * | status_data | ) |

Here is the call graph for this function:

◆ clear_unaccessible_dimm_data()

| void clear_unaccessible_dimm_data | ( | uint8_t | dimm_id | ) |

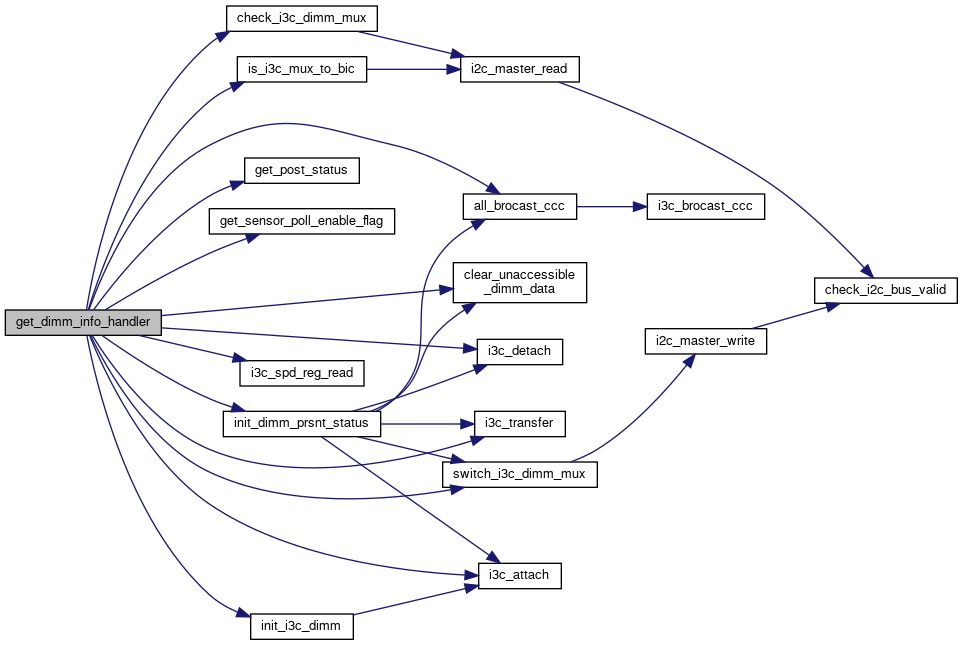

◆ get_dimm_info_handler()

| void get_dimm_info_handler | ( | ) |

Here is the call graph for this function:

◆ get_dimm_present()

| uint8_t get_dimm_present | ( | uint8_t | dimm_id | ) |

◆ get_spd_raw_ready()

| bool get_spd_raw_ready | ( | uint8_t | dimm_id | ) |

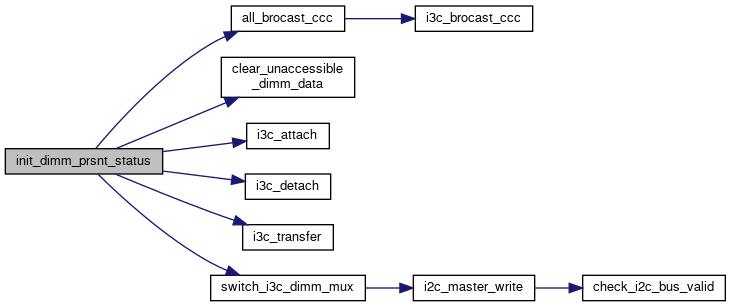

◆ init_dimm_prsnt_status()

| int init_dimm_prsnt_status | ( | ) |

Here is the call graph for this function:

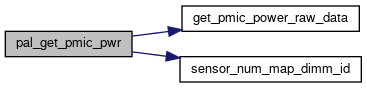

◆ pal_get_pmic_pwr()

| int pal_get_pmic_pwr | ( | uint8_t | sensor_num, |

| uint8_t * | data | ||

| ) |

Here is the call graph for this function:

◆ pal_get_spd_temp()

| int pal_get_spd_temp | ( | uint8_t | sensor_num, |

| uint8_t * | data | ||

| ) |

Here is the call graph for this function:

◆ plat_get_spd_raw()

| int plat_get_spd_raw | ( | uint8_t | dimm_id, |

| uint8_t ** | buf_out, | ||

| bool * | ready_out | ||

| ) |

◆ sensor_num_map_dimm_id()

| uint8_t sensor_num_map_dimm_id | ( | uint8_t | sensor_num | ) |

◆ set_spd_raw_ready()

| void set_spd_raw_ready | ( | uint8_t | dimm_id, |

| bool | ready | ||

| ) |

◆ start_get_dimm_info_thread()

| void start_get_dimm_info_thread | ( | ) |

Here is the call graph for this function:

◆ switch_i3c_dimm_mux()

| int switch_i3c_dimm_mux | ( | uint8_t | i3c_ctrl_mux_data | ) |

Here is the call graph for this function:

Variable Documentation

◆ i3c_dimm_mutex

|

extern |

◆ pmic_i3c_addr_list

|

extern |

◆ spd_i3c_addr_list

|

extern |