#include <logging/log.h>#include "plat_util.h"#include "plat_pldm_sensor.h"#include "plat_vr_test_mode.h"#include "plat_hook.h"#include "plat_class.h"

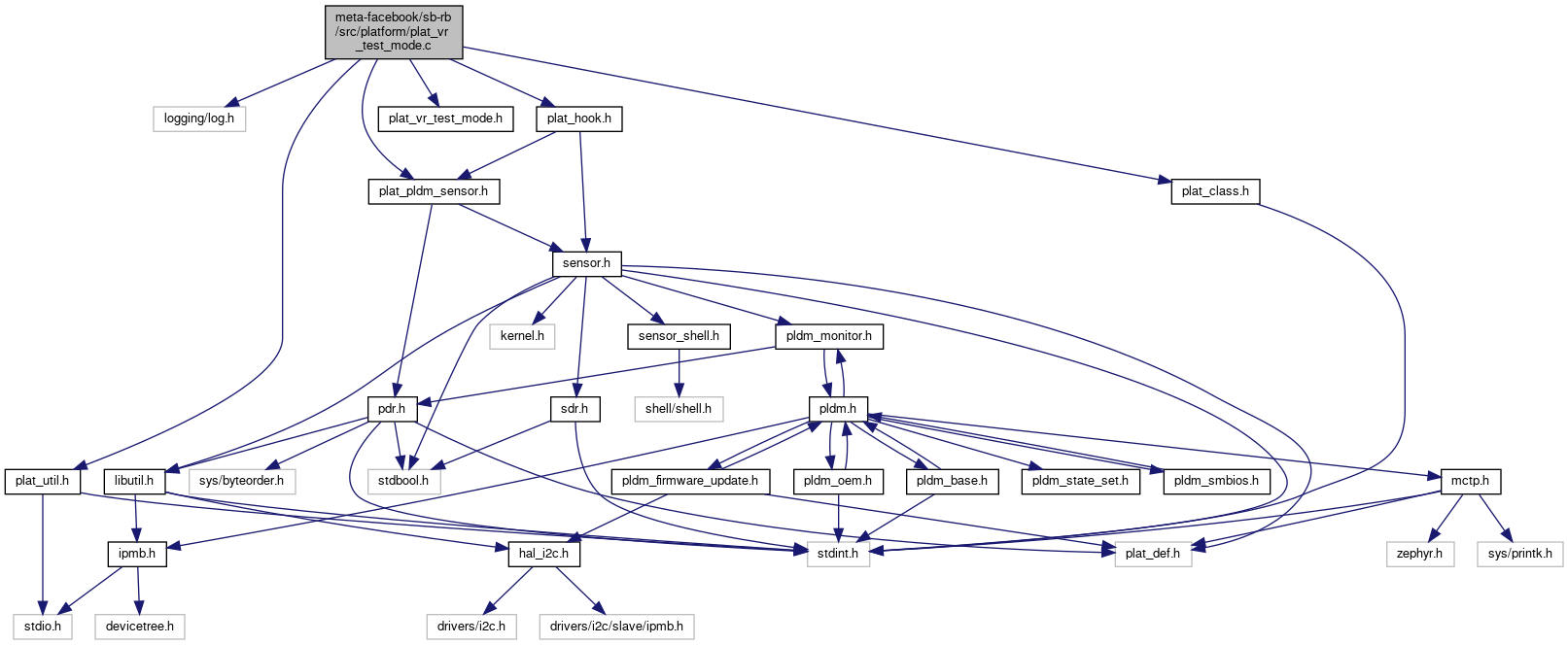

Include dependency graph for plat_vr_test_mode.c:

Functions | |

| LOG_MODULE_REGISTER (plat_vr_test_mode) | |

| K_KERNEL_STACK_MEMBER (vr_test_mode_thread_stack, 512) | |

| bool | get_vr_test_mode_flag (void) |

| bool | update_vr_reg (uint8_t rail, uint8_t reg, uint16_t val) |

| bool | dma_write_vr (uint8_t rail, uint16_t reg, uint8_t *data, uint8_t len) |

| bool | dma_read_vr (uint8_t rail, uint16_t reg, uint8_t *data, uint8_t len) |

| bool | get_vr_offset_uvp_ovp (uint8_t rail, uint16_t *uvp, uint16_t *ovp) |

| bool | use_offset_uvp_ovp (uint8_t rail) |

| bool | get_vr_fixed_uvp_ovp_enable (uint8_t rail) |

| bool | set_vr_fixed_uvp_ovp_enable (uint8_t rail, uint8_t enable) |

| void | vr_test_mode_enable (bool onoff) |

| void | vr_test_mode_handler (void *arg1, void *arg2, void *arg3) |

| void | init_vr_test_mode_polling (void) |

Variables | |

| struct k_thread | vr_test_mode_thread |

| k_tid_t | vr_test_mode_tid |

| bool | vr_test_mode_flag = false |

| const vr_test_mode_setting_t | vr_test_mode_table [] |

| const vr_test_mode_setting_t | vr_test_mode_table_default [] |

| const mps_vr_test_mode_setting_t | vr_mps_test_mode_table [] |

| const mps_vr_test_mode_setting_t | vr_mps_normal_mode_table [] |

| const uint8_t | vr_test_mode_table_size = ARRAY_SIZE(vr_test_mode_table) |

| const uint8_t | vr_test_mode_table_dafault_size = ARRAY_SIZE(vr_test_mode_table_default) |

| const uint8_t | vr_mps_test_mode_table_size = ARRAY_SIZE(vr_mps_test_mode_table) |

| const uint8_t | vr_mps_normal_mode_table_size = ARRAY_SIZE(vr_mps_normal_mode_table) |

Function Documentation

◆ dma_read_vr()

| bool dma_read_vr | ( | uint8_t | rail, |

| uint16_t | reg, | ||

| uint8_t * | data, | ||

| uint8_t | len | ||

| ) |

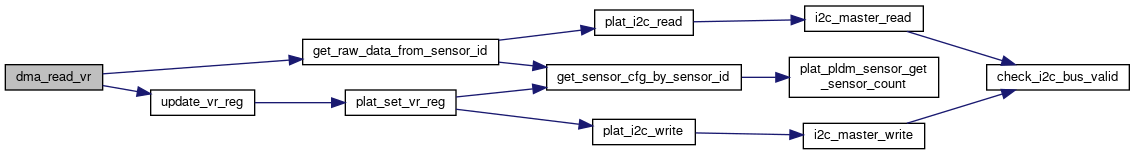

Here is the call graph for this function:

◆ dma_write_vr()

| bool dma_write_vr | ( | uint8_t | rail, |

| uint16_t | reg, | ||

| uint8_t * | data, | ||

| uint8_t | len | ||

| ) |

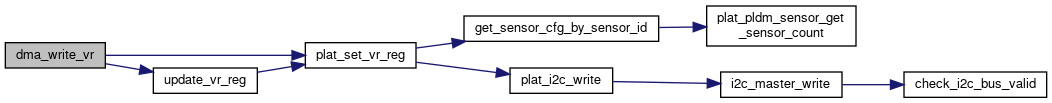

Here is the call graph for this function:

◆ get_vr_fixed_uvp_ovp_enable()

| bool get_vr_fixed_uvp_ovp_enable | ( | uint8_t | rail | ) |

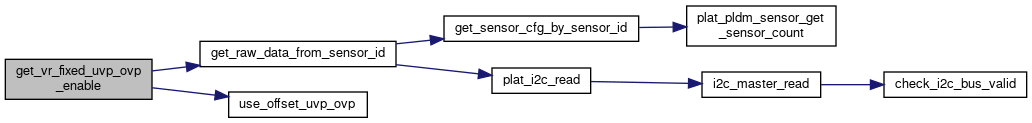

Here is the call graph for this function:

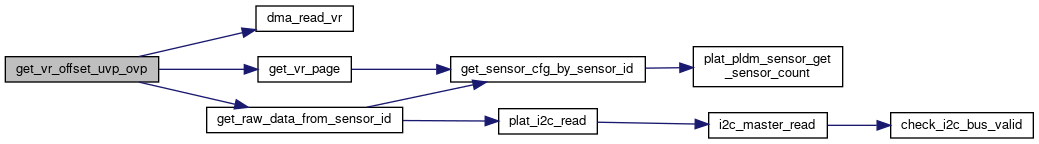

◆ get_vr_offset_uvp_ovp()

| bool get_vr_offset_uvp_ovp | ( | uint8_t | rail, |

| uint16_t * | uvp, | ||

| uint16_t * | ovp | ||

| ) |

Here is the call graph for this function:

◆ get_vr_test_mode_flag()

| bool get_vr_test_mode_flag | ( | void | ) |

◆ init_vr_test_mode_polling()

| void init_vr_test_mode_polling | ( | void | ) |

Here is the call graph for this function:

◆ K_KERNEL_STACK_MEMBER()

| K_KERNEL_STACK_MEMBER | ( | vr_test_mode_thread_stack | , |

| 512 | |||

| ) |

◆ LOG_MODULE_REGISTER()

| LOG_MODULE_REGISTER | ( | plat_vr_test_mode | ) |

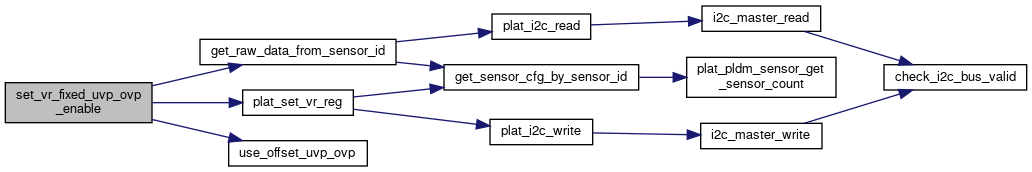

◆ set_vr_fixed_uvp_ovp_enable()

| bool set_vr_fixed_uvp_ovp_enable | ( | uint8_t | rail, |

| uint8_t | enable | ||

| ) |

Here is the call graph for this function:

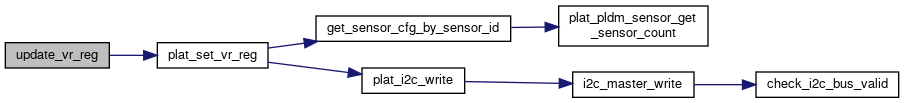

◆ update_vr_reg()

| bool update_vr_reg | ( | uint8_t | rail, |

| uint8_t | reg, | ||

| uint16_t | val | ||

| ) |

Here is the call graph for this function:

◆ use_offset_uvp_ovp()

| bool use_offset_uvp_ovp | ( | uint8_t | rail | ) |

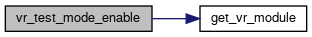

◆ vr_test_mode_enable()

| void vr_test_mode_enable | ( | bool | onoff | ) |

Here is the call graph for this function:

◆ vr_test_mode_handler()

| void vr_test_mode_handler | ( | void * | arg1, |

| void * | arg2, | ||

| void * | arg3 | ||

| ) |

Variable Documentation

◆ vr_mps_normal_mode_table

| const mps_vr_test_mode_setting_t vr_mps_normal_mode_table[] |

◆ vr_mps_normal_mode_table_size

| const uint8_t vr_mps_normal_mode_table_size = ARRAY_SIZE(vr_mps_normal_mode_table) |

◆ vr_mps_test_mode_table

| const mps_vr_test_mode_setting_t vr_mps_test_mode_table[] |

◆ vr_mps_test_mode_table_size

| const uint8_t vr_mps_test_mode_table_size = ARRAY_SIZE(vr_mps_test_mode_table) |

◆ vr_test_mode_flag

| bool vr_test_mode_flag = false |

◆ vr_test_mode_table

| const vr_test_mode_setting_t vr_test_mode_table[] |

Initial value:

= {

{ VR_RAIL_E_ASIC_P0V85_MEDHA0_VDD, 14300, 14300, 200, 940, 930, 595, 930, 0 },

{ VR_RAIL_E_ASIC_P0V85_MEDHA1_VDD, 14300, 14300, 200, 940, 930, 595, 930, 0 },

{ VR_RAIL_E_ASIC_P0V9_OWL_E_TRVDD, 170, 170, 200, 1130, 1120, 630, 1120, 0 },

{ VR_RAIL_E_ASIC_P0V75_OWL_E_TRVDD, 110, 110, 200, 1130, 975, 525, 975, 0 },

{ VR_RAIL_E_ASIC_P0V75_MAX_M_VDD, 1200, 1200, 200, 1130, 975, 525, 975, 0 },

{ VR_RAIL_E_ASIC_P0V75_VDDPHY_HBM1357, 1500, 1500, 200, 940, 930, 525, 930, 0 },

{ VR_RAIL_E_ASIC_P0V75_OWL_E_VDD, 1600, 1600, 200, 940, 930, 525, 930, 0 },

{ VR_RAIL_E_ASIC_P0V4_VDDQL_HBM1357, 530, 530, 200, 800, 520, 280, 520, 0 },

{ VR_RAIL_E_ASIC_P1V1_VDDQC_HBM1357, 3200, 3200, 200, 1320, 1310, 770, 1310, 0 },

{ VR_RAIL_E_ASIC_P1V8_VPP_HBM1357, 140, 140, 200, 1980, 1970, 1260, 1970, 0 },

{ VR_RAIL_E_ASIC_P0V75_MAX_N_VDD, 670, 670, 200, 1130, 975, 525, 975, 0 },

{ VR_RAIL_E_ASIC_P0V8_HAMSA_AVDD_PCIE, 500, 500, 200, 1130, 1040, 560, 1040, 0 },

{ VR_RAIL_E_ASIC_P1V2_HAMSA_VDDHRXTX_PCIE, 100, 100, 200, 1320, 1310, 840, 1310, 0 },

{ VR_RAIL_E_ASIC_P0V85_HAMSA_VDD, 1000, 1000, 200, 1063, 1053, 595, 1053, 0 },

{ VR_RAIL_E_ASIC_P1V1_VDDQC_HBM0246, 3200, 3200, 200, 1320, 1310, 770, 1310, 0 },

{ VR_RAIL_E_ASIC_P1V8_VPP_HBM0246, 140, 140, 200, 1980, 1970, 1260, 1970, 0 },

{ VR_RAIL_E_ASIC_P0V4_VDDQL_HBM0246, 530, 530, 200, 800, 520, 280, 520, 0 },

{ VR_RAIL_E_ASIC_P0V75_VDDPHY_HBM0246, 1500, 1500, 200, 940, 930, 525, 930, 0 },

{ VR_RAIL_E_ASIC_P0V75_OWL_W_VDD, 1600, 1500, 200, 940, 930, 525, 930, 0 },

{ VR_RAIL_E_ASIC_P0V75_MAX_S_VDD, 660, 660, 200, 1130, 975, 525, 975, 0 },

{ VR_RAIL_E_ASIC_P0V9_OWL_W_TRVDD, 170, 170, 200, 1130, 1120, 630, 1120, 0 },

{ VR_RAIL_E_ASIC_P0V75_OWL_W_TRVDD, 110, 110, 200, 1130, 975, 525, 975, 0 },

}

@ VR_RAIL_E_ASIC_P1V2_HAMSA_VDDHRXTX_PCIE

Definition: plat_hook.h:61

◆ vr_test_mode_table_dafault_size

| const uint8_t vr_test_mode_table_dafault_size = ARRAY_SIZE(vr_test_mode_table_default) |

◆ vr_test_mode_table_default

| const vr_test_mode_setting_t vr_test_mode_table_default[] |

Initial value:

= {

{ VR_RAIL_E_ASIC_P0V85_MEDHA0_VDD, 14300, 14300, 640, 940, 918, 782, 918, 870 },

{ VR_RAIL_E_ASIC_P0V85_MEDHA1_VDD, 14300, 14300, 640, 940, 918, 782, 918, 870 },

{ VR_RAIL_E_ASIC_P0V9_OWL_E_TRVDD, 170, 160, 700, 1010, 954, 846, 954, 900 },

{ VR_RAIL_E_ASIC_P0V75_OWL_E_TRVDD, 110, 100, 575, 910, 795, 705, 795, 750 },

{ VR_RAIL_E_ASIC_P0V75_MAX_M_VDD, 670, 570, 575, 910, 848, 690, 848, 785 },

{ VR_RAIL_E_ASIC_P0V75_VDDPHY_HBM1357, 1230, 1130, 575, 910, 795, 705, 795, 758 },

{ VR_RAIL_E_ASIC_P0V75_OWL_E_VDD, 1600, 1500, 575, 910, 810, 690, 810, 750 },

{ VR_RAIL_E_ASIC_P0V4_VDDQL_HBM1357, 460, 360, 325, 800, 440, 380, 440, 408 },

{ VR_RAIL_E_ASIC_P1V1_VDDQC_HBM1357, 2800, 2700, 900, 1260, 1177, 1067, 1177, 1100 },

{ VR_RAIL_E_ASIC_P1V8_VPP_HBM1357, 140, 140, 1400, 1960, 1950, 1746, 1950, 1815 },

{ VR_RAIL_E_ASIC_P0V75_MAX_N_VDD, 670, 570, 575, 910, 848, 690, 848, 780 },

{ VR_RAIL_E_ASIC_P0V8_HAMSA_AVDD_PCIE, 500, 400, 635, 940, 848, 752, 848, 846 },

{ VR_RAIL_E_ASIC_P1V2_HAMSA_VDDHRXTX_PCIE, 100, 90, 1000, 1300, 1272, 1128, 1272, 1225 },

{ VR_RAIL_E_ASIC_P0V85_HAMSA_VDD, 850, 750, 640, 940, 918, 782, 918, 865 },

{ VR_RAIL_E_ASIC_P1V1_VDDQC_HBM0246, 2800, 2700, 900, 1260, 1177, 1067, 1177, 1100 },

{ VR_RAIL_E_ASIC_P1V8_VPP_HBM0246, 140, 140, 1400, 1960, 1950, 1746, 1950, 1815 },

{ VR_RAIL_E_ASIC_P0V4_VDDQL_HBM0246, 460, 360, 325, 800, 440, 380, 440, 407 },

{ VR_RAIL_E_ASIC_P0V75_VDDPHY_HBM0246, 1230, 1130, 575, 910, 795, 705, 795, 766 },

{ VR_RAIL_E_ASIC_P0V75_OWL_W_VDD, 1600, 1500, 575, 910, 810, 690, 810, 755 },

{ VR_RAIL_E_ASIC_P0V75_MAX_S_VDD, 580, 480, 575, 910, 848, 690, 848, 795 },

{ VR_RAIL_E_ASIC_P0V9_OWL_W_TRVDD, 170, 160, 700, 1010, 954, 846, 954, 900 },

{ VR_RAIL_E_ASIC_P0V75_OWL_W_TRVDD, 110, 100, 575, 910, 795, 705, 795, 750 },

}

◆ vr_test_mode_table_size

| const uint8_t vr_test_mode_table_size = ARRAY_SIZE(vr_test_mode_table) |

◆ vr_test_mode_thread

| struct k_thread vr_test_mode_thread |

◆ vr_test_mode_tid

| k_tid_t vr_test_mode_tid |