shell_iris_power.c File Reference

#include <stdlib.h>#include <shell/shell.h>#include "plat_cpld.h"#include <logging/log.h>#include <shell_plat_power_sequence.h>#include "plat_gpio.h"#include "plat_isr.h"#include "plat_i2c.h"#include "plat_ioexp.h"#include "plat_pldm_sensor.h"#include "plat_class.h"#include "shell_iris_power.h"

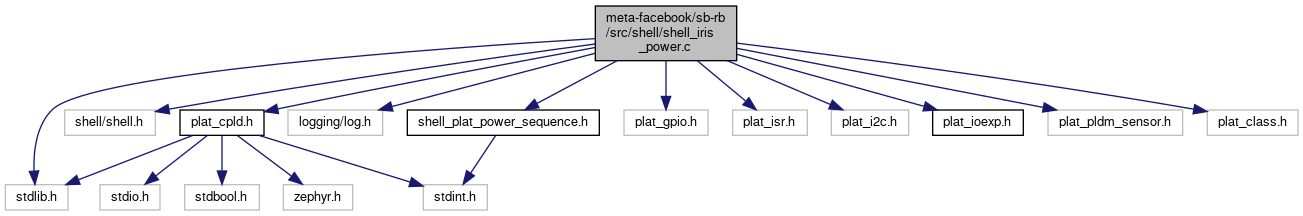

Include dependency graph for shell_iris_power.c:

Classes | |

| struct | power_good_status |

| struct | steps_on_struct |

| struct | pwr_clock_compnt_mapping |

| struct | ioe_power_good_status |

| struct | ioe_pwr_on |

Macros | |

| #define | enable 0x01 |

| #define | disable 0x00 |

| #define | NO_DEFINED 0xFF |

| #define | CLK_BUF_U85_ADDR (0xCE >> 1) |

| #define | CLK_BUF_U87_ADDR (0xD8 >> 1) |

| #define | CLK_BUF_U88_ADDR (0xDE >> 1) |

| #define | CLK_GEN_100M_U86_ADDR 0x9 |

| #define | CLK_BUF_100M_WRITE_LOCK_CLEAR_LOS_EVENT_OFFSET 0x27 |

| #define | CLK_GEN_LOSMON_EVENT_OFFSET 0x5a |

| #define | CLK_BUF_100M_BYTE_COUNT 0x7 |

| #define | MAX_STEPS (sizeof(steps_on) / sizeof(steps_on[0])) |

Typedefs | |

| typedef struct power_good_status | power_good_status |

| typedef struct steps_on_struct | steps_on_struct |

| typedef struct pwr_clock_compnt_mapping | pwr_clock_compnt_mapping |

| typedef struct ioe_power_good_status | ioe_power_good_status |

| typedef struct ioe_pwr_on | ioe_pwr_on |

Functions | |

| LOG_MODULE_REGISTER (shell_iris_power) | |

| void | clear_clock_status (const struct shell *shell, uint8_t clock_index) |

| bool | check_p3v3_p5v_pwrgd (void) |

| void | power_on_p3v3_osfp () |

| void | power_off_p3v3_osfp (const struct shell *shell) |

| void | pwer_gd_get_status (const struct shell *shell) |

| void | steps_on_p3v3_osfp (const struct shell *shell) |

| void | pwr_get_clock_status (const struct shell *shell, uint8_t clock_index) |

| void | cmd_iris_power_on (const struct shell *shell, size_t argc, char **argv) |

| void | cmd_iris_power_off (const struct shell *shell, size_t argc, char **argv) |

| void | cmd_iris_power_cycle (const struct shell *shell, size_t argc, char **argv) |

| void | cmd_iris_steps_on (const struct shell *shell, size_t argc, char **argv) |

| void | cmd_iris_disable_steps_on (const struct shell *shell, size_t argc, char **argv) |

| SHELL_STATIC_SUBCMD_SET_CREATE (sub_iris_power_cmd, SHELL_CMD(on, NULL, "iris power on", cmd_iris_power_on), SHELL_CMD(off, NULL, "iris power off", cmd_iris_power_off), SHELL_CMD(cycle, NULL, "iris power cycle", cmd_iris_power_cycle), SHELL_CMD(steps_on, NULL, "iris power steps_on", cmd_iris_steps_on), SHELL_CMD(disable_steps_on, NULL, "iris power disable steps_on", cmd_iris_disable_steps_on), SHELL_SUBCMD_SET_END) | |

| SHELL_CMD_REGISTER (iris_power, &sub_iris_power_cmd, "iris power commands", NULL) | |

Macro Definition Documentation

◆ CLK_BUF_100M_BYTE_COUNT

| #define CLK_BUF_100M_BYTE_COUNT 0x7 |

◆ CLK_BUF_100M_WRITE_LOCK_CLEAR_LOS_EVENT_OFFSET

| #define CLK_BUF_100M_WRITE_LOCK_CLEAR_LOS_EVENT_OFFSET 0x27 |

◆ CLK_BUF_U85_ADDR

| #define CLK_BUF_U85_ADDR (0xCE >> 1) |

◆ CLK_BUF_U87_ADDR

| #define CLK_BUF_U87_ADDR (0xD8 >> 1) |

◆ CLK_BUF_U88_ADDR

| #define CLK_BUF_U88_ADDR (0xDE >> 1) |

◆ CLK_GEN_100M_U86_ADDR

| #define CLK_GEN_100M_U86_ADDR 0x9 |

◆ CLK_GEN_LOSMON_EVENT_OFFSET

| #define CLK_GEN_LOSMON_EVENT_OFFSET 0x5a |

◆ disable

| #define disable 0x00 |

◆ enable

| #define enable 0x01 |

◆ MAX_STEPS

| #define MAX_STEPS (sizeof(steps_on) / sizeof(steps_on[0])) |

◆ NO_DEFINED

| #define NO_DEFINED 0xFF |

Typedef Documentation

◆ ioe_power_good_status

| typedef struct ioe_power_good_status ioe_power_good_status |

◆ ioe_pwr_on

| typedef struct ioe_pwr_on ioe_pwr_on |

◆ power_good_status

| typedef struct power_good_status power_good_status |

◆ pwr_clock_compnt_mapping

| typedef struct pwr_clock_compnt_mapping pwr_clock_compnt_mapping |

◆ steps_on_struct

| typedef struct steps_on_struct steps_on_struct |

Enumeration Type Documentation

◆ power_good_status_type_for_steps_on

Function Documentation

◆ check_p3v3_p5v_pwrgd()

| bool check_p3v3_p5v_pwrgd | ( | void | ) |

Here is the call graph for this function:

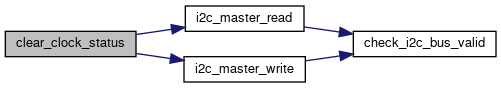

◆ clear_clock_status()

| void clear_clock_status | ( | const struct shell * | shell, |

| uint8_t | clock_index | ||

| ) |

Here is the call graph for this function:

◆ cmd_iris_disable_steps_on()

| void cmd_iris_disable_steps_on | ( | const struct shell * | shell, |

| size_t | argc, | ||

| char ** | argv | ||

| ) |

Here is the call graph for this function:

◆ cmd_iris_power_cycle()

| void cmd_iris_power_cycle | ( | const struct shell * | shell, |

| size_t | argc, | ||

| char ** | argv | ||

| ) |

◆ cmd_iris_power_off()

| void cmd_iris_power_off | ( | const struct shell * | shell, |

| size_t | argc, | ||

| char ** | argv | ||

| ) |

◆ cmd_iris_power_on()

| void cmd_iris_power_on | ( | const struct shell * | shell, |

| size_t | argc, | ||

| char ** | argv | ||

| ) |

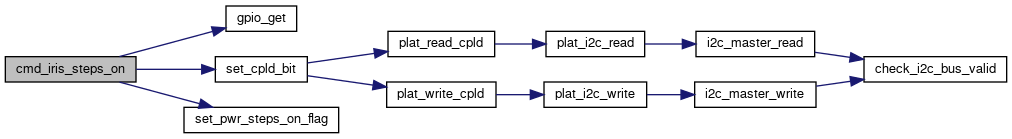

◆ cmd_iris_steps_on()

| void cmd_iris_steps_on | ( | const struct shell * | shell, |

| size_t | argc, | ||

| char ** | argv | ||

| ) |

Here is the call graph for this function:

◆ LOG_MODULE_REGISTER()

| LOG_MODULE_REGISTER | ( | shell_iris_power | ) |

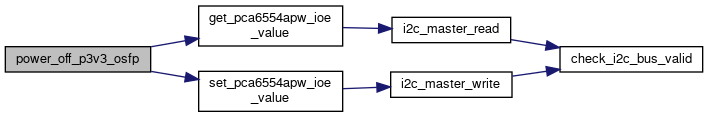

◆ power_off_p3v3_osfp()

| void power_off_p3v3_osfp | ( | const struct shell * | shell | ) |

Here is the call graph for this function:

◆ power_on_p3v3_osfp()

| void power_on_p3v3_osfp | ( | ) |

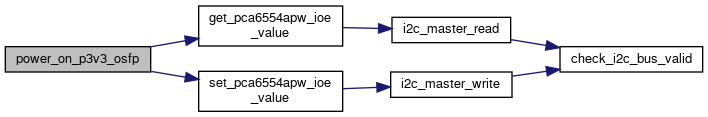

Here is the call graph for this function:

◆ pwer_gd_get_status()

| void pwer_gd_get_status | ( | const struct shell * | shell | ) |

Here is the call graph for this function:

◆ pwr_get_clock_status()

| void pwr_get_clock_status | ( | const struct shell * | shell, |

| uint8_t | clock_index | ||

| ) |

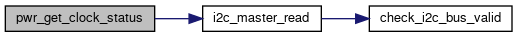

Here is the call graph for this function:

◆ SHELL_CMD_REGISTER()

| SHELL_CMD_REGISTER | ( | iris_power | , |

| & | sub_iris_power_cmd, | ||

| "iris power commands" | , | ||

| NULL | |||

| ) |

◆ SHELL_STATIC_SUBCMD_SET_CREATE()

| SHELL_STATIC_SUBCMD_SET_CREATE | ( | sub_iris_power_cmd | , |

| SHELL_CMD(on, NULL, "iris power on", cmd_iris_power_on) | , | ||

| SHELL_CMD(off, NULL, "iris power off", cmd_iris_power_off) | , | ||

| SHELL_CMD(cycle, NULL, "iris power cycle", cmd_iris_power_cycle) | , | ||

| SHELL_CMD(steps_on, NULL, "iris power steps_on", cmd_iris_steps_on) | , | ||

| SHELL_CMD(disable_steps_on, NULL, "iris power disable steps_on", cmd_iris_disable_steps_on) | , | ||

| SHELL_SUBCMD_SET_END | |||

| ) |

◆ steps_on_p3v3_osfp()

| void steps_on_p3v3_osfp | ( | const struct shell * | shell | ) |

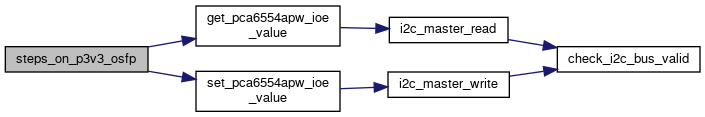

Here is the call graph for this function:

Variable Documentation

◆ ioe_pwr_on_table

| ioe_pwr_on ioe_pwr_on_table[] |

Initial value:

= {

}

◆ ioe_pwrgd_status_table

| ioe_power_good_status ioe_pwrgd_status_table[] |

Initial value:

= {

}

◆ power_good_status_table_for_steps_on

| power_good_status power_good_status_table_for_steps_on[] |

◆ power_steps

| int power_steps = 0 |

◆ pwr_clock_compnt_mapping_table

| pwr_clock_compnt_mapping pwr_clock_compnt_mapping_table[] |

Initial value:

= {

}