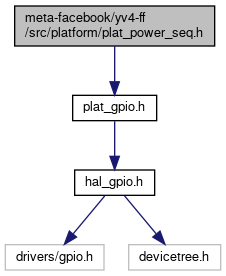

Go to the source code of this file.

|

| enum | POWER_ON_STAGE {

BOARD_POWER_ON_STAGE0 = 0x00

, BOARD_POWER_ON_STAGE1

, BOARD_POWER_ON_STAGE2

, RETIMER_POWER_ON_STAGE0

,

RETIMER_POWER_ON_STAGE1

, RETIMER_POWER_ON_STAGE2

, E1S_POWER_ON_STAGE0

, E1S_POWER_ON_STAGE1

,

E1S_POWER_ON_STAGE2

, E1S_POWER_ON_STAGE3

, ASIC_POWER_ON_STAGE1 = 0x00

, ASIC_POWER_ON_STAGE2

,

DIMM_POWER_ON_STAGE1

, DIMM_POWER_ON_STAGE2

, DIMM_POWER_ON_STAGE3

, ASIC_POWER_ON_STAGE = 0x00

,

DIMM_POWER_ON_STAGE1

, DIMM_POWER_ON_STAGE2

, DIMM_POWER_ON_STAGE3

, BOARD_POWER_ON_STAGE

,

CLK_POWER_ON_STAGE = 0

, ASIC_POWER_ON_STAGE_1

, ASIC_POWER_ON_STAGE_2

, DIMM_POWER_ON_STAGE_1

,

DIMM_POWER_ON_STAGE_2

, DIMM_POWER_ON_STAGE_3

, MAX_POWER_ON_STAGES

, ASIC_POWER_ON_STAGE_1 = 0

,

CLK_POWER_ON_STAGE

, ASIC_POWER_ON_STAGE_2

, ASIC_POWER_ON_STAGE_3

, DIMM_POWER_ON_STAGE_1

,

DIMM_POWER_ON_STAGE_2

, DIMM_POWER_ON_STAGE_3

, MAX_POWER_ON_STAGES

} |

| |

| enum | POWER_OFF_STAGE {

E1S_POWER_OFF_STAGE0 = 0x00

, E1S_POWER_OFF_STAGE1

, E1S_POWER_OFF_STAGE2

, E1S_POWER_OFF_STAGE3

,

RETIMER_POWER_OFF_STAGE0

, RETIMER_POWER_OFF_STAGE1

, RETIMER_POWER_OFF_STAGE2

, BOARD_POWER_OFF_STAGE0

,

BOARD_POWER_OFF_STAGE1

, BOARD_POWER_OFF_STAGE2

, DIMM_POWER_OFF_STAGE1 = 0x00

, DIMM_POWER_OFF_STAGE2

,

DIMM_POWER_OFF_STAGE3

, ASIC_POWER_OFF_STAGE1

, ASIC_POWER_OFF_STAGE2

, BOARD_POWER_OFF_STAGE

,

DIMM_POWER_OFF_STAGE1 = 0x00

, DIMM_POWER_OFF_STAGE2

, DIMM_POWER_OFF_STAGE3

, ASIC_POWER_OFF_STAGE1

,

ASIC_POWER_OFF_STAGE2

, BOARD_POWER_OFF_STAGE

, DIMM_POWER_OFF_STAGE_1 = 0

, DIMM_POWER_OFF_STAGE_2

,

DIMM_POWER_OFF_STAGE_3

, ASIC_POWER_OFF_STAGE_1

, ASIC_POWER_OFF_STAGE_2

, ASIC_POWER_OFF_STAGE_3

,

CLK_POWER_OFF_STAGE

, MAX_POWER_OFF_STAGES

, DIMM_POWER_OFF_STAGE_1 = 0

, DIMM_POWER_OFF_STAGE_2

,

DIMM_POWER_OFF_STAGE_3

, ASIC_POWER_OFF_STAGE_1

, ASIC_POWER_OFF_STAGE_2

, ASIC_POWER_OFF_STAGE_3

,

CLK_POWER_OFF_STAGE

, MAX_POWER_OFF_STAGES

} |

| |

◆ CHK_PWR_DELAY_MSEC

| #define CHK_PWR_DELAY_MSEC 100 |

◆ CXL_HEART_BEAT_LABEL

| #define CXL_HEART_BEAT_LABEL "HB0" |

◆ CXL_READY_INTERVAL_SECONDS

| #define CXL_READY_INTERVAL_SECONDS 3 |

◆ CXL_READY_RETRY_TIMES

| #define CXL_READY_RETRY_TIMES 10 |

◆ DC_ON_DELAY5_SEC

| #define DC_ON_DELAY5_SEC 5 |

◆ P1V8_POWER_OFF_DELAY_MSEC

| #define P1V8_POWER_OFF_DELAY_MSEC 3500 |

◆ PWR_ON_RST_DELAY_MSEC

| #define PWR_ON_RST_DELAY_MSEC 25 |

◆ SYS_CLK_STABLE_DELAY_MSEC

| #define SYS_CLK_STABLE_DELAY_MSEC 25 |

◆ POWER_OFF_STAGE

| Enumerator |

|---|

| E1S_POWER_OFF_STAGE0 | |

| E1S_POWER_OFF_STAGE1 | |

| E1S_POWER_OFF_STAGE2 | |

| E1S_POWER_OFF_STAGE3 | |

| RETIMER_POWER_OFF_STAGE0 | |

| RETIMER_POWER_OFF_STAGE1 | |

| RETIMER_POWER_OFF_STAGE2 | |

| BOARD_POWER_OFF_STAGE0 | |

| BOARD_POWER_OFF_STAGE1 | |

| BOARD_POWER_OFF_STAGE2 | |

| DIMM_POWER_OFF_STAGE1 | |

| DIMM_POWER_OFF_STAGE2 | |

| DIMM_POWER_OFF_STAGE3 | |

| ASIC_POWER_OFF_STAGE1 | |

| ASIC_POWER_OFF_STAGE2 | |

| BOARD_POWER_OFF_STAGE | |

| DIMM_POWER_OFF_STAGE1 | |

| DIMM_POWER_OFF_STAGE2 | |

| DIMM_POWER_OFF_STAGE3 | |

| ASIC_POWER_OFF_STAGE1 | |

| ASIC_POWER_OFF_STAGE2 | |

| BOARD_POWER_OFF_STAGE | |

| DIMM_POWER_OFF_STAGE_1 | |

| DIMM_POWER_OFF_STAGE_2 | |

| DIMM_POWER_OFF_STAGE_3 | |

| ASIC_POWER_OFF_STAGE_1 | |

| ASIC_POWER_OFF_STAGE_2 | |

| ASIC_POWER_OFF_STAGE_3 | |

| CLK_POWER_OFF_STAGE | |

| MAX_POWER_OFF_STAGES | |

| DIMM_POWER_OFF_STAGE_1 | |

| DIMM_POWER_OFF_STAGE_2 | |

| DIMM_POWER_OFF_STAGE_3 | |

| ASIC_POWER_OFF_STAGE_1 | |

| ASIC_POWER_OFF_STAGE_2 | |

| ASIC_POWER_OFF_STAGE_3 | |

| CLK_POWER_OFF_STAGE | |

| MAX_POWER_OFF_STAGES | |

◆ POWER_ON_STAGE

| Enumerator |

|---|

| BOARD_POWER_ON_STAGE0 | |

| BOARD_POWER_ON_STAGE1 | |

| BOARD_POWER_ON_STAGE2 | |

| RETIMER_POWER_ON_STAGE0 | |

| RETIMER_POWER_ON_STAGE1 | |

| RETIMER_POWER_ON_STAGE2 | |

| E1S_POWER_ON_STAGE0 | |

| E1S_POWER_ON_STAGE1 | |

| E1S_POWER_ON_STAGE2 | |

| E1S_POWER_ON_STAGE3 | |

| ASIC_POWER_ON_STAGE1 | |

| ASIC_POWER_ON_STAGE2 | |

| DIMM_POWER_ON_STAGE1 | |

| DIMM_POWER_ON_STAGE2 | |

| DIMM_POWER_ON_STAGE3 | |

| ASIC_POWER_ON_STAGE | |

| DIMM_POWER_ON_STAGE1 | |

| DIMM_POWER_ON_STAGE2 | |

| DIMM_POWER_ON_STAGE3 | |

| BOARD_POWER_ON_STAGE | |

| CLK_POWER_ON_STAGE | |

| ASIC_POWER_ON_STAGE_1 | |

| ASIC_POWER_ON_STAGE_2 | |

| DIMM_POWER_ON_STAGE_1 | |

| DIMM_POWER_ON_STAGE_2 | |

| DIMM_POWER_ON_STAGE_3 | |

| MAX_POWER_ON_STAGES | |

| ASIC_POWER_ON_STAGE_1 | |

| CLK_POWER_ON_STAGE | |

| ASIC_POWER_ON_STAGE_2 | |

| ASIC_POWER_ON_STAGE_3 | |

| DIMM_POWER_ON_STAGE_1 | |

| DIMM_POWER_ON_STAGE_2 | |

| DIMM_POWER_ON_STAGE_3 | |

| MAX_POWER_ON_STAGES | |

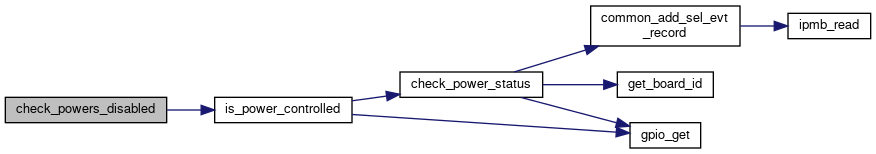

◆ check_powers_disabled()

| int check_powers_disabled |

( |

uint8_t |

pwr_stage | ) |

|

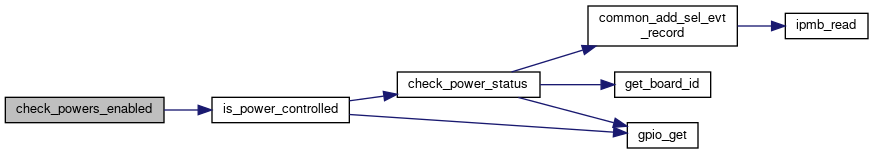

◆ check_powers_enabled()

| int check_powers_enabled |

( |

uint8_t |

pwr_stage | ) |

|

◆ cxl_ready_access()

| bool cxl_ready_access |

( |

uint8_t |

sensor_num | ) |

|

◆ cxl_ready_handler()

| void cxl_ready_handler |

( |

| ) |

|

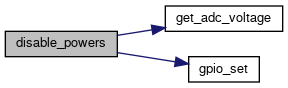

◆ disable_powers()

| void disable_powers |

( |

uint8_t |

pwr_stage | ) |

|

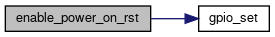

◆ enable_power_on_rst()

| void enable_power_on_rst |

( |

| ) |

|

◆ enable_powers()

| void enable_powers |

( |

uint8_t |

pwr_stage | ) |

|

◆ execute_power_off_sequence()

| void execute_power_off_sequence |

( |

| ) |

|

◆ execute_power_on_sequence()

| void execute_power_on_sequence |

( |

| ) |

|

◆ get_cxl_ready_status()

| bool get_cxl_ready_status |

( |

| ) |

|

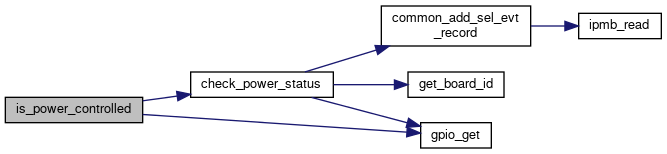

◆ is_power_controlled()

| bool is_power_controlled |

( |

uint8_t |

power_pin, |

|

|

uint8_t |

check_power_status, |

|

|

char * |

power_name |

|

) |

| |

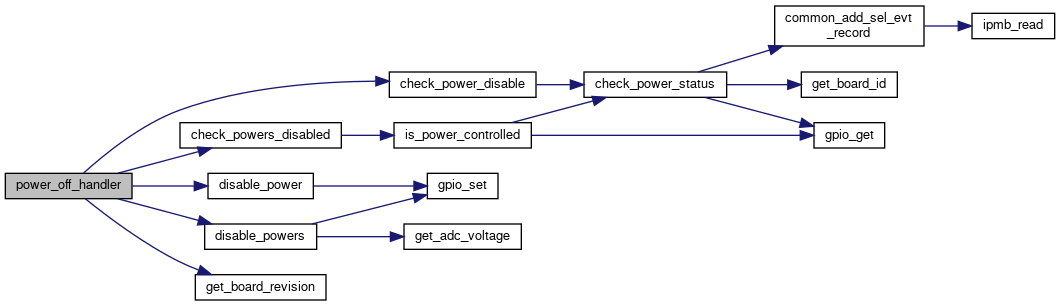

◆ power_off_handler()

| int power_off_handler |

( |

uint8_t |

power_stage | ) |

|

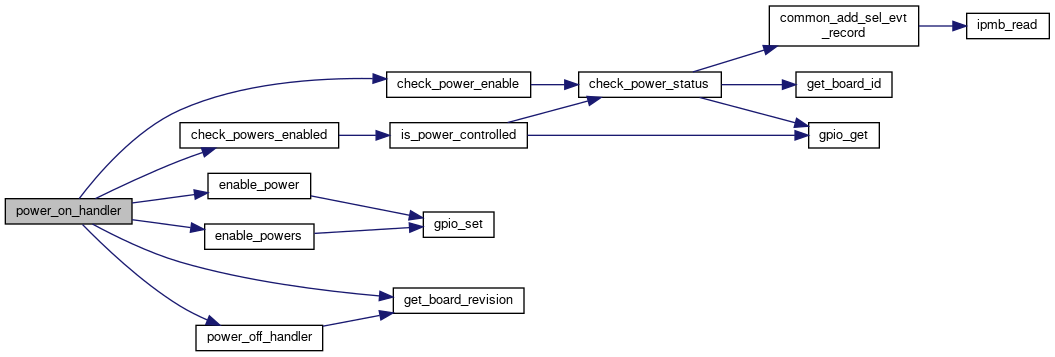

◆ power_on_handler()

| int power_on_handler |

( |

uint8_t |

power_stage | ) |

|

◆ set_mb_dc_status()

| void set_mb_dc_status |

( |

uint8_t |

gpio_num | ) |

|