shell_plat_soc_pwron_reset.c File Reference

#include <shell/shell.h>#include <stdlib.h>#include <logging/log.h>#include <string.h>#include "plat_isr.h"#include "plat_i2c.h"#include "plat_cpld.h"

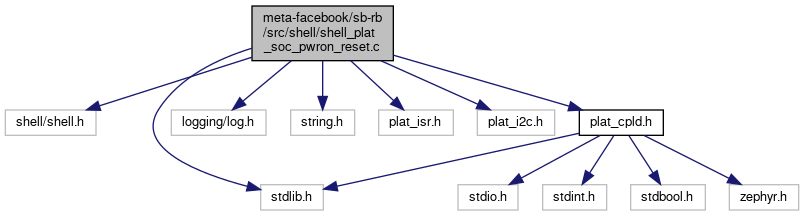

Include dependency graph for shell_plat_soc_pwron_reset.c:

Classes | |

| struct | soc_pwron_reset_item_t |

Macros | |

| #define | IRIS_POWER_RESET_OFFSET 0x00 |

| #define | IRIS_BOARD_POWER_ENABLE 0xFF |

| #define | IRIS_BOARD_POWER_DISABLE 0xC7 |

| #define | HAMSA_POWER_ON_RESET_BIT 5 |

| #define | MEDHA0_POWER_ON_RESET_BIT 4 |

| #define | MEDHA1_POWER_ON_RESET_BIT 3 |

| #define | HAMSA_SYS_RST_BIT 2 |

| #define | MEDHA0_SYS_RST_BIT 1 |

| #define | MEDHA1_SYS_RST_BIT 0 |

| #define | RESET_BASE_MASK 0xC0 /* 1100_0000 */ |

| #define | RESET_ON_BYTE(orig, bit) ((uint8_t)((orig) | (1u << (bit)) | RESET_BASE_MASK)) |

| #define | RESET_OFF_BYTE(orig, bit) ((uint8_t)(((orig) & ~(1u << (bit))) | RESET_BASE_MASK)) |

Enumerations | |

| enum | soc_pwron_reset_id_t { HAMSA_POWER_ON_RESET_L_ID = 0 , MEDHA0_POWER_ON_RESET_L_ID , MEDHA1_POWER_ON_RESET_L_ID , HAMSA_SYS_RST_L_ID , MEDHA0_SYS_RST_L_ID , MEDHA1_SYS_RST_L_ID , SOC_PWRON_RESET_MAX_ID } |

Functions | |

| LOG_MODULE_REGISTER (plat_soc_pwron_reset_shell) | |

| bool | soc_pwron_reset_name_get (uint8_t idx, uint8_t **name) |

| SHELL_DYNAMIC_CMD_CREATE (oc_pwron_reset_name, soc_pwron_reset_rname_get_) | |

| SHELL_STATIC_SUBCMD_SET_CREATE (sub_soc_pwron_reset_cmds, SHELL_CMD_ARG(override, NULL, "soc_pwron_reset override <drive-level>", cmd_soc_pwron_reset_override, 2, 1), SHELL_CMD(passthru, NULL, "soc_pwron_reset passthru", cmd_soc_pwron_reset_override), SHELL_CMD(get, NULL, "soc_pwron_reset get all | get <NAME>", cmd_soc_pwron_reset_get), SHELL_CMD(set, &oc_pwron_reset_name, "soc_pwron_reset set <NAME> <0|1>", cmd_soc_pwron_reset_set), SHELL_SUBCMD_SET_END) | |

| SHELL_CMD_REGISTER (soc_pwron_reset, &sub_soc_pwron_reset_cmds, "soc_pwron_reset commands", NULL) | |

Macro Definition Documentation

◆ HAMSA_POWER_ON_RESET_BIT

| #define HAMSA_POWER_ON_RESET_BIT 5 |

◆ HAMSA_SYS_RST_BIT

| #define HAMSA_SYS_RST_BIT 2 |

◆ IRIS_BOARD_POWER_DISABLE

| #define IRIS_BOARD_POWER_DISABLE 0xC7 |

◆ IRIS_BOARD_POWER_ENABLE

| #define IRIS_BOARD_POWER_ENABLE 0xFF |

◆ IRIS_POWER_RESET_OFFSET

| #define IRIS_POWER_RESET_OFFSET 0x00 |

◆ MEDHA0_POWER_ON_RESET_BIT

| #define MEDHA0_POWER_ON_RESET_BIT 4 |

◆ MEDHA0_SYS_RST_BIT

| #define MEDHA0_SYS_RST_BIT 1 |

◆ MEDHA1_POWER_ON_RESET_BIT

| #define MEDHA1_POWER_ON_RESET_BIT 3 |

◆ MEDHA1_SYS_RST_BIT

| #define MEDHA1_SYS_RST_BIT 0 |

◆ RESET_BASE_MASK

| #define RESET_BASE_MASK 0xC0 /* 1100_0000 */ |

◆ RESET_OFF_BYTE

| #define RESET_OFF_BYTE | ( | orig, | |

| bit | |||

| ) | ((uint8_t)(((orig) & ~(1u << (bit))) | RESET_BASE_MASK)) |

◆ RESET_ON_BYTE

| #define RESET_ON_BYTE | ( | orig, | |

| bit | |||

| ) | ((uint8_t)((orig) | (1u << (bit)) | RESET_BASE_MASK)) |

Enumeration Type Documentation

◆ soc_pwron_reset_id_t

| enum soc_pwron_reset_id_t |

Function Documentation

◆ LOG_MODULE_REGISTER()

| LOG_MODULE_REGISTER | ( | plat_soc_pwron_reset_shell | ) |

◆ SHELL_CMD_REGISTER()

| SHELL_CMD_REGISTER | ( | soc_pwron_reset | , |

| & | sub_soc_pwron_reset_cmds, | ||

| "soc_pwron_reset commands" | , | ||

| NULL | |||

| ) |

◆ SHELL_DYNAMIC_CMD_CREATE()

| SHELL_DYNAMIC_CMD_CREATE | ( | oc_pwron_reset_name | , |

| soc_pwron_reset_rname_get_ | |||

| ) |

◆ SHELL_STATIC_SUBCMD_SET_CREATE()

| SHELL_STATIC_SUBCMD_SET_CREATE | ( | sub_soc_pwron_reset_cmds | , |

| SHELL_CMD_ARG(override, NULL, "soc_pwron_reset override <drive-level>", cmd_soc_pwron_reset_override, 2, 1) | , | ||

| SHELL_CMD(passthru, NULL, "soc_pwron_reset passthru", cmd_soc_pwron_reset_override) | , | ||

| SHELL_CMD(get, NULL, "soc_pwron_reset get all | get <NAME>", cmd_soc_pwron_reset_get) | , | ||

| SHELL_CMD(set, &oc_pwron_reset_name, "soc_pwron_reset set <NAME> <0|1>", cmd_soc_pwron_reset_set) | , | ||

| SHELL_SUBCMD_SET_END | |||

| ) |

◆ soc_pwron_reset_name_get()

| bool soc_pwron_reset_name_get | ( | uint8_t | idx, |

| uint8_t ** | name | ||

| ) |