#include <stdint.h>

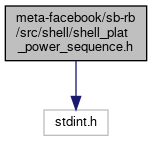

Include dependency graph for shell_plat_power_sequence.h:

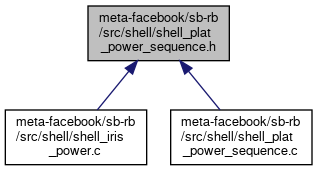

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | power_sequence |

| struct | power_sequence_event_pwrgd |

Typedefs | |

| typedef struct power_sequence | power_sequence |

| typedef struct power_sequence_event_pwrgd | power_sequence_event_pwrgd |

Functions | |

| bool | plat_find_power_seq_fail () |

| uint8_t | plat_get_power_seq_fail_id () |

| void | plat_get_power_seq_fail_name (uint8_t idx, uint8_t **name) |

| void | plat_get_power_seq_pwrgd_event_fail_name (uint8_t idx, uint8_t **name) |

| uint8_t | get_pwrgd_sequence_fail_sensor_num () |

Macro Definition Documentation

◆ FM_CLK_48MHZ_EN_DOWN_REG

| #define FM_CLK_48MHZ_EN_DOWN_REG 0x83 |

◆ FM_IRIS_CLK_100MHZ_EN_N_DOWN_REG

| #define FM_IRIS_CLK_100MHZ_EN_N_DOWN_REG 0x82 |

◆ FM_IRIS_CLK_312MHZ_EN_N_DOWN_REG

| #define FM_IRIS_CLK_312MHZ_EN_N_DOWN_REG 0x84 |

◆ FM_P3V3_CLK_DOWN_REG

| #define FM_P3V3_CLK_DOWN_REG 0xB0 |

◆ FM_P3V3_CLK_ON_REG

| #define FM_P3V3_CLK_ON_REG 0xAD |

◆ HAMSA_AVDD_PCIE_DOWN_REG

| #define HAMSA_AVDD_PCIE_DOWN_REG 0x7B |

◆ HAMSA_AVDD_PCIE_ON_REG

| #define HAMSA_AVDD_PCIE_ON_REG 0x64 |

◆ HAMSA_POWER_ON_RESET_PLD_L_ON_REG

| #define HAMSA_POWER_ON_RESET_PLD_L_ON_REG 0x6D |

◆ HAMSA_SYS_RST_PLD_L_ON_REG

| #define HAMSA_SYS_RST_PLD_L_ON_REG 0x70 |

◆ HAMSA_VDD_DOWN_REG

| #define HAMSA_VDD_DOWN_REG 0x96 |

◆ HAMSA_VDD_ON_REG

| #define HAMSA_VDD_ON_REG 0x49 |

◆ HAMSA_VDDHRXTX_PCIE_DOWN_REG

| #define HAMSA_VDDHRXTX_PCIE_DOWN_REG 0x74 |

◆ HAMSA_VDDHRXTX_PCIE_ON_REG

| #define HAMSA_VDDHRXTX_PCIE_ON_REG 0x6B |

◆ IRIS_CLK_100MHZ_ON_REG

| #define IRIS_CLK_100MHZ_ON_REG 0x5B |

◆ IRIS_CLK_312_5_MHZ_ON_REG

| #define IRIS_CLK_312_5_MHZ_ON_REG 0x5D |

◆ IRIS_CLK_48MHZ_ON_REG

| #define IRIS_CLK_48MHZ_ON_REG 0x5C |

◆ LDO_IN_1V2_DOWN_REG

| #define LDO_IN_1V2_DOWN_REG 0x99 |

◆ LDO_IN_1V2_ON_REG

| #define LDO_IN_1V2_ON_REG 0x46 |

◆ MAX_M_VDD_DOWN_REG

| #define MAX_M_VDD_DOWN_REG 0x91 |

◆ MAX_M_VDD_ON_REG

| #define MAX_M_VDD_ON_REG 0x4E |

◆ MAX_N_VDD_DOWN_REG

| #define MAX_N_VDD_DOWN_REG 0x90 |

◆ MAX_N_VDD_ON_REG

| #define MAX_N_VDD_ON_REG 0x4F |

◆ MAX_S_VDD_DOWN_REG

| #define MAX_S_VDD_DOWN_REG 0x8F |

◆ MAX_S_VDD_ON_REG

| #define MAX_S_VDD_ON_REG 0x50 |

◆ MEDHA0_POWER_ON_RESET_PLD_L_ON_REG

| #define MEDHA0_POWER_ON_RESET_PLD_L_ON_REG 0x6E |

◆ MEDHA0_SYS_RST_PLD_L_ON_REG

| #define MEDHA0_SYS_RST_PLD_L_ON_REG 0x71 |

◆ MEDHA0_VDD_DOWN_REG

| #define MEDHA0_VDD_DOWN_REG 0x94 |

◆ MEDHA0_VDD_ON_REG

| #define MEDHA0_VDD_ON_REG 0x4B |

◆ MEDHA1_POWER_ON_RESET_PLD_L_ON_REG

| #define MEDHA1_POWER_ON_RESET_PLD_L_ON_REG 0x6F |

◆ MEDHA1_SYS_RST_PLD_L_ON_REG

| #define MEDHA1_SYS_RST_PLD_L_ON_REG 0x72 |

◆ MEDHA1_VDD_DOWN_REG

| #define MEDHA1_VDD_DOWN_REG 0x95 |

◆ MEDHA1_VDD_ON_REG

| #define MEDHA1_VDD_ON_REG 0x4A |

◆ NO_SENSOR_NUM

| #define NO_SENSOR_NUM 0xFF |

◆ OWL_E_PVDD0P9_ON_REG

| #define OWL_E_PVDD0P9_ON_REG 0x67 |

◆ OWL_E_RVDD1P5_ON_REG

| #define OWL_E_RVDD1P5_ON_REG 0x69 |

◆ OWL_E_TRVDD0P75_DOWN_REG

| #define OWL_E_TRVDD0P75_DOWN_REG 0x8D |

◆ OWL_E_TRVDD0P75_ON_REG

| #define OWL_E_TRVDD0P75_ON_REG 0x51 |

◆ OWL_E_TRVDD0P9_DOWN_REG

| #define OWL_E_TRVDD0P9_DOWN_REG 0x79 |

◆ OWL_E_TRVDD0P9_ON_REG

| #define OWL_E_TRVDD0P9_ON_REG 0x65 |

◆ OWL_E_VDD_DOWN_REG

| #define OWL_E_VDD_DOWN_REG 0x92 |

◆ OWL_E_VDD_ON_REG

| #define OWL_E_VDD_ON_REG 0x4C |

◆ OWL_W_PVDD0P9_ON_REG

| #define OWL_W_PVDD0P9_ON_REG 0x68 |

◆ OWL_W_RVDD1P5_ON_REG

| #define OWL_W_RVDD1P5_ON_REG 0x6A |

◆ OWL_W_TRVDD0P75_DOWN_REG

| #define OWL_W_TRVDD0P75_DOWN_REG 0x8E |

◆ OWL_W_TRVDD0P75_ON_REG

| #define OWL_W_TRVDD0P75_ON_REG 0x52 |

◆ OWL_W_TRVDD0P9_DOWN_REG

| #define OWL_W_TRVDD0P9_DOWN_REG 0x7A |

◆ OWL_W_TRVDD0P9_ON_REG

| #define OWL_W_TRVDD0P9_ON_REG 0x66 |

◆ OWL_W_VDD_DOWN_REG

| #define OWL_W_VDD_DOWN_REG 0x93 |

◆ OWL_W_VDD_ON_REG

| #define OWL_W_VDD_ON_REG 0x4D |

◆ P0V75_AVDD_HCSL_DOWN_REG

| #define P0V75_AVDD_HCSL_DOWN_REG 0x97 |

◆ P0V75_AVDD_HCSL_ON_REG

| #define P0V75_AVDD_HCSL_ON_REG 0x48 |

◆ P0V9_OWL_E_PVDD_DOWN_REG

| #define P0V9_OWL_E_PVDD_DOWN_REG 0x77 |

◆ P0V9_OWL_W_PVDD_DOWN_REG

| #define P0V9_OWL_W_PVDD_DOWN_REG 0x78 |

◆ P12V_ON_REG

| #define P12V_ON_REG 0x43 |

◆ P12V_UBC_DOWN_REG

| #define P12V_UBC_DOWN_REG 0x9C |

◆ P1V5_E_RVDD_DOWN_REG

| #define P1V5_E_RVDD_DOWN_REG 0x75 |

◆ P1V5_PLL_VDDA_OWL_E_DOWN_REG

| #define P1V5_PLL_VDDA_OWL_E_DOWN_REG 0x8A |

◆ P1V5_PLL_VDDA_OWL_E_ON_REG

| #define P1V5_PLL_VDDA_OWL_E_ON_REG 0x55 |

◆ P1V5_PLL_VDDA_OWL_W_DOWN_REG

| #define P1V5_PLL_VDDA_OWL_W_DOWN_REG 0xAF |

◆ P1V5_PLL_VDDA_OWL_W_ON_REG

| #define P1V5_PLL_VDDA_OWL_W_ON_REG 0xAC |

◆ P1V5_PLL_VDDA_SOC_DOWN_REG

| #define P1V5_PLL_VDDA_SOC_DOWN_REG 0x89 |

◆ P1V5_PLL_VDDA_SOC_ON_REG

| #define P1V5_PLL_VDDA_SOC_ON_REG 0x56 |

◆ P1V5_W_RVDD_DOWN_REG

| #define P1V5_W_RVDD_DOWN_REG 0x76 |

◆ P1V8_DOWN_REG

| #define P1V8_DOWN_REG 0x98 |

◆ P1V8_ON_REG

| #define P1V8_ON_REG 0x47 |

◆ P3V3_DOWN_REG

| #define P3V3_DOWN_REG 0x9B |

◆ P3V3_ON_REG

| #define P3V3_ON_REG 0x44 |

◆ P4V2_DOWN_REG

| #define P4V2_DOWN_REG 0xAE |

◆ P4V2_ON_REG

| #define P4V2_ON_REG 0xAB |

◆ P5V_DOWN_REG

| #define P5V_DOWN_REG 0x9A |

◆ P5V_ON_REG

| #define P5V_ON_REG 0x45 |

◆ PERST_DELAY_DOWN_REG

| #define PERST_DELAY_DOWN_REG 0x9D |

◆ PLL_VDDA15_HBM0_HBM2_DOWN_REG

| #define PLL_VDDA15_HBM0_HBM2_DOWN_REG 0x85 |

◆ PLL_VDDA15_HBM0_HBM2_ON_REG

| #define PLL_VDDA15_HBM0_HBM2_ON_REG 0x57 |

◆ PLL_VDDA15_HBM1_HBM3_DOWN_REG

| #define PLL_VDDA15_HBM1_HBM3_DOWN_REG 0x86 |

◆ PLL_VDDA15_HBM1_HBM3_ON_REG

| #define PLL_VDDA15_HBM1_HBM3_ON_REG 0x58 |

◆ PLL_VDDA15_HBM4_HBM6_DOWN_REG

| #define PLL_VDDA15_HBM4_HBM6_DOWN_REG 0x87 |

◆ PLL_VDDA15_HBM4_HBM6_ON_REG

| #define PLL_VDDA15_HBM4_HBM6_ON_REG 0x59 |

◆ PLL_VDDA15_HBM5_HBM7_DOWN_REG

| #define PLL_VDDA15_HBM5_HBM7_DOWN_REG 0x88 |

◆ PLL_VDDA15_HBM5_HBM7_ON_REG

| #define PLL_VDDA15_HBM5_HBM7_ON_REG 0x5A |

◆ PVDD1P5_DOWN_REG

| #define PVDD1P5_DOWN_REG 0x73 |

◆ PVDD1P5_ON_REG

| #define PVDD1P5_ON_REG 0x6C |

◆ VDDPHY_HBM0_HBM2_HBM4_HBM6_DOWN_REG

| #define VDDPHY_HBM0_HBM2_HBM4_HBM6_DOWN_REG 0x8B |

◆ VDDPHY_HBM0_HBM2_HBM4_HBM6_ON_REG

| #define VDDPHY_HBM0_HBM2_HBM4_HBM6_ON_REG 0x53 |

◆ VDDPHY_HBM1_HBM3_HBM5_HBM7_DOWN_REG

| #define VDDPHY_HBM1_HBM3_HBM5_HBM7_DOWN_REG 0x8C |

◆ VDDPHY_HBM1_HBM3_HBM5_HBM7_ON_REG

| #define VDDPHY_HBM1_HBM3_HBM5_HBM7_ON_REG 0x54 |

◆ VDDQC_HBM0_HBM2_HBM4_HBM6_DOWN_REG

| #define VDDQC_HBM0_HBM2_HBM4_HBM6_DOWN_REG 0x7E |

◆ VDDQC_HBM0_HBM2_HBM4_HBM6_ON_REG

| #define VDDQC_HBM0_HBM2_HBM4_HBM6_ON_REG 0x60 |

◆ VDDQC_HBM1_HBM3_HBM5_HBM7_DOWN_REG

| #define VDDQC_HBM1_HBM3_HBM5_HBM7_DOWN_REG 0x7F |

◆ VDDQC_HBM1_HBM3_HBM5_HBM7_ON_REG

| #define VDDQC_HBM1_HBM3_HBM5_HBM7_ON_REG 0x61 |

◆ VDDQL_HBM0_HBM2_HBM4_HBM6_DOWN_REG

| #define VDDQL_HBM0_HBM2_HBM4_HBM6_DOWN_REG 0x7C |

◆ VDDQL_HBM0_HBM2_HBM4_HBM6_ON_REG

| #define VDDQL_HBM0_HBM2_HBM4_HBM6_ON_REG 0x62 |

◆ VDDQL_HBM1_HBM3_HBM5_HBM7_DOWN_REG

| #define VDDQL_HBM1_HBM3_HBM5_HBM7_DOWN_REG 0x7D |

◆ VDDQL_HBM1_HBM3_HBM5_HBM7_ON_REG

| #define VDDQL_HBM1_HBM3_HBM5_HBM7_ON_REG 0x63 |

◆ VPP_HBM0_HBM2_HBM4_HBM6_DOWN_REG

| #define VPP_HBM0_HBM2_HBM4_HBM6_DOWN_REG 0x80 |

◆ VPP_HBM0_HBM2_HBM4_HBM6_ON_REG

| #define VPP_HBM0_HBM2_HBM4_HBM6_ON_REG 0x5E |

◆ VPP_HBM1_HBM3_HBM5_HBM7_DOWN_REG

| #define VPP_HBM1_HBM3_HBM5_HBM7_DOWN_REG 0x81 |

◆ VPP_HBM1_HBM3_HBM5_HBM7_ON_REG

| #define VPP_HBM1_HBM3_HBM5_HBM7_ON_REG 0x5F |

Typedef Documentation

◆ power_sequence

| typedef struct power_sequence power_sequence |

◆ power_sequence_event_pwrgd

| typedef struct power_sequence_event_pwrgd power_sequence_event_pwrgd |

Function Documentation

◆ get_pwrgd_sequence_fail_sensor_num()

| uint8_t get_pwrgd_sequence_fail_sensor_num | ( | ) |

◆ plat_find_power_seq_fail()

| bool plat_find_power_seq_fail | ( | ) |

Here is the call graph for this function:

◆ plat_get_power_seq_fail_id()

| uint8_t plat_get_power_seq_fail_id | ( | ) |

◆ plat_get_power_seq_fail_name()

| void plat_get_power_seq_fail_name | ( | uint8_t | idx, |

| uint8_t ** | name | ||

| ) |

◆ plat_get_power_seq_pwrgd_event_fail_name()

| void plat_get_power_seq_pwrgd_event_fail_name | ( | uint8_t | idx, |

| uint8_t ** | name | ||

| ) |