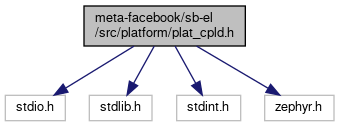

#include <stdio.h>

#include <stdlib.h>

#include <stdint.h>

#include <zephyr.h>

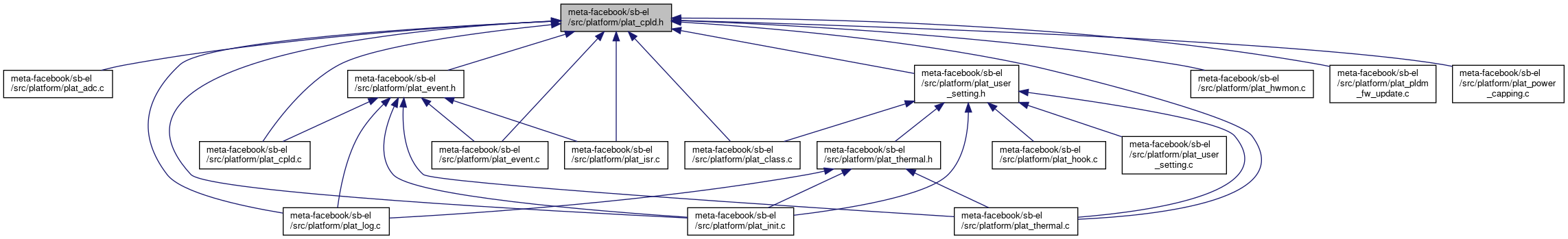

Go to the source code of this file.

◆ ASIC_JTAG_MUX_SEL

| #define ASIC_JTAG_MUX_SEL 0x39 |

◆ ASIC_TEMP_OVER_REG

| #define ASIC_TEMP_OVER_REG 0x29 |

◆ ASIC_VR_HOT_SWITCH

| #define ASIC_VR_HOT_SWITCH 0x12 |

◆ CPLD_ASIC_RESET_STATUS_REG

| #define CPLD_ASIC_RESET_STATUS_REG 0xA2 |

◆ CPLD_OFFSE_MANUAL_CONTROL_STRAP

| #define CPLD_OFFSE_MANUAL_CONTROL_STRAP 0xB2 |

◆ CPLD_OFFSET_ADC_IDX

| #define CPLD_OFFSET_ADC_IDX 0xA0 |

◆ CPLD_OFFSET_ASIC_BOARD_ID

| #define CPLD_OFFSET_ASIC_BOARD_ID 0x3C |

◆ CPLD_OFFSET_ASIC_RESET

| #define CPLD_OFFSET_ASIC_RESET 0x00 |

◆ CPLD_OFFSET_ASIC_RST_DELAY

| #define CPLD_OFFSET_ASIC_RST_DELAY 0xA4 |

◆ CPLD_OFFSET_BOARD_REV_ID

| #define CPLD_OFFSET_BOARD_REV_ID 0x14 |

◆ CPLD_OFFSET_MMC_PWR_EN

| #define CPLD_OFFSET_MMC_PWR_EN 0x38 |

◆ CPLD_OFFSET_MODULE_PG_DELAY

| #define CPLD_OFFSET_MODULE_PG_DELAY 0xA5 |

◆ CPLD_OFFSET_POWER_CAPPING_LV1_TIME

| #define CPLD_OFFSET_POWER_CAPPING_LV1_TIME 0x36 |

◆ CPLD_OFFSET_POWER_CLAMP

| #define CPLD_OFFSET_POWER_CLAMP 0x25 |

◆ CPLD_OFFSET_USERCODE

| #define CPLD_OFFSET_USERCODE 0x32 |

◆ CPLD_OFFSET_VR_VENDER_TYPE

| #define CPLD_OFFSET_VR_VENDER_TYPE 0x15 |

◆ CPLD_PERST_DELAY_0_REG

| #define CPLD_PERST_DELAY_0_REG 0x9D |

◆ CPLD_PERST_DELAY_1_REG

| #define CPLD_PERST_DELAY_1_REG 0xB3 |

◆ CPLD_PERST_DELAY_2_REG

| #define CPLD_PERST_DELAY_2_REG 0xB4 |

◆ CPLD_PERST_DELAY_3_REG

| #define CPLD_PERST_DELAY_3_REG 0xB5 |

◆ CPLD_POWER_INFO_0_REG [1/2]

| #define CPLD_POWER_INFO_0_REG 0xB6 |

◆ CPLD_POWER_INFO_0_REG [2/2]

| #define CPLD_POWER_INFO_0_REG 0xB6 |

◆ CPLD_POWER_INFO_1_REG [1/2]

| #define CPLD_POWER_INFO_1_REG 0xB7 |

◆ CPLD_POWER_INFO_1_REG [2/2]

| #define CPLD_POWER_INFO_1_REG 0xB7 |

◆ HAMSA_CONTROL_IO

| #define HAMSA_CONTROL_IO 0x18 |

◆ HAMSA_JTAG_JTCE

| #define HAMSA_JTAG_JTCE 0x19 |

◆ HAMSA_MFIO12_13_14_CTRL

| #define HAMSA_MFIO12_13_14_CTRL 0xB8 |

◆ HAMSA_MFIO12_13_14_INPUT

| #define HAMSA_MFIO12_13_14_INPUT 0xBA |

◆ HAMSA_MFIO_REG

| #define HAMSA_MFIO_REG 0x17 |

◆ HAMSA_STRAP

◆ HBM_CATTRIP_LOG_REG

| #define HBM_CATTRIP_LOG_REG 0x27 |

◆ HBM_CATTRIP_REG

| #define HBM_CATTRIP_REG 0x27 |

◆ LEAK_DETECT_REG

| #define LEAK_DETECT_REG 0x24 |

◆ NUWA0_CONTROL_IO

| #define NUWA0_CONTROL_IO 0x1B |

◆ NUWA0_STRAP

◆ NUWA1_CONTROL_IO

| #define NUWA1_CONTROL_IO 0x1D |

◆ NUWA1_STRAP

◆ NUWA_JTAG_JTCE

| #define NUWA_JTAG_JTCE 0x1F |

◆ NUWA_MFIO12_13_14_CTRL

| #define NUWA_MFIO12_13_14_CTRL 0xB9 |

◆ NUWA_MFIO12_13_14_INPUT

| #define NUWA_MFIO12_13_14_INPUT 0xBB |

◆ NUWA_MFIO_REG

| #define NUWA_MFIO_REG 0x1E |

◆ OWL_CONTROL_IO

| #define OWL_CONTROL_IO 0x20 |

◆ OWL_DVT_ENABLE

| #define OWL_DVT_ENABLE 0x9E |

◆ OWL_JTAG_SEL

| #define OWL_JTAG_SEL 0x21 |

◆ OWL_UART_SEL

| #define OWL_UART_SEL 0x22 |

◆ PWRGD_EVENT_LATCH_1_REG

| #define PWRGD_EVENT_LATCH_1_REG 0xBE |

◆ PWRGD_EVENT_LATCH_2_REG

| #define PWRGD_EVENT_LATCH_2_REG 0xBF |

◆ PWRGD_EVENT_LATCH_3_REG

| #define PWRGD_EVENT_LATCH_3_REG 0xC0 |

◆ PWRGD_EVENT_LATCH_4_REG

| #define PWRGD_EVENT_LATCH_4_REG 0xC1 |

◆ PWRGD_EVENT_LATCH_5_REG

| #define PWRGD_EVENT_LATCH_5_REG 0xC2 |

◆ PWRGD_EVENT_LATCH_6_REG

| #define PWRGD_EVENT_LATCH_6_REG 0xC3 |

◆ SYSTEM_ALERT_FAULT_REG

| #define SYSTEM_ALERT_FAULT_REG 0x28 |

◆ TEMP_IC_OVER_FAULT_REG

| #define TEMP_IC_OVER_FAULT_REG 0x2A |

◆ TMP75_ALERT_CPLD_OFFSET

| #define TMP75_ALERT_CPLD_OFFSET 0x2F |

◆ VR_1_EN

◆ VR_1STEP_FUNC_EN_REG

| #define VR_1STEP_FUNC_EN_REG 0xA9 |

◆ VR_2_EN

◆ VR_3_EN

◆ VR_4_EN

◆ VR_AND_CLK_EN

| #define VR_AND_CLK_EN 0x3E |

◆ VR_AND_CLK_EN_PIN_CTRL

| #define VR_AND_CLK_EN_PIN_CTRL 0xA1 |

◆ VR_EN_PIN_READING_5

| #define VR_EN_PIN_READING_5 0x05 |

◆ VR_POWER_FAULT_1_REG

| #define VR_POWER_FAULT_1_REG 0x0D |

◆ VR_POWER_FAULT_2_REG

| #define VR_POWER_FAULT_2_REG 0x0E |

◆ VR_POWER_FAULT_3_REG

| #define VR_POWER_FAULT_3_REG 0x0F |

◆ VR_POWER_FAULT_4_REG

| #define VR_POWER_FAULT_4_REG 0x10 |

◆ VR_POWER_FAULT_5_REG

| #define VR_POWER_FAULT_5_REG 0x11 |

◆ VR_PWRGD_PIN_READING_1_REG

| #define VR_PWRGD_PIN_READING_1_REG 0x07 |

◆ VR_PWRGD_PIN_READING_2_REG

| #define VR_PWRGD_PIN_READING_2_REG 0x08 |

◆ VR_PWRGD_PIN_READING_3_REG

| #define VR_PWRGD_PIN_READING_3_REG 0x09 |

◆ VR_PWRGD_PIN_READING_4_REG

| #define VR_PWRGD_PIN_READING_4_REG 0x0A |

◆ VR_PWRGD_PIN_READING_5_REG

| #define VR_PWRGD_PIN_READING_5_REG 0x0B |

◆ VR_PWRGD_PIN_READING_6_REG

| #define VR_PWRGD_PIN_READING_6_REG 0x0C |

◆ VR_SMBUS_ALERT_EVENT_LOG_REG

| #define VR_SMBUS_ALERT_EVENT_LOG_REG 0x26 |

◆ cpld_info

◆ get_cpld_polling_power_info()

| void get_cpld_polling_power_info |

( |

int * |

reading | ) |

|

◆ init_cpld_polling()

| void init_cpld_polling |

( |

void |

| ) |

|

◆ plat_read_cpld()

| bool plat_read_cpld |

( |

uint8_t |

offset, |

|

|

uint8_t * |

data, |

|

|

uint8_t |

len |

|

) |

| |

◆ plat_write_cpld()

| bool plat_write_cpld |

( |

uint8_t |

offset, |

|

|

uint8_t * |

data |

|

) |

| |

◆ reset_error_log_states()

| void reset_error_log_states |

( |

uint8_t |

err_type | ) |

|

◆ set_cpld_bit()

| bool set_cpld_bit |

( |

uint8_t |

cpld_offset, |

|

|

uint8_t |

bit, |

|

|

uint8_t |

value |

|

) |

| |

◆ set_cpld_polling_enable_flag()

| void set_cpld_polling_enable_flag |

( |

bool |

status | ) |

|