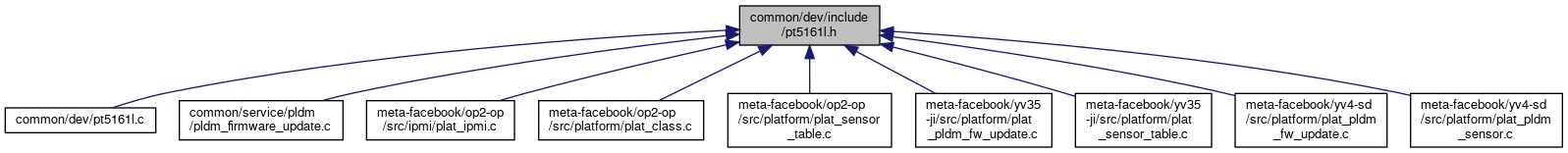

Go to the source code of this file.

◆ PCIE_RETIMER_UPDATE_MAX_OFFSET

| #define PCIE_RETIMER_UPDATE_MAX_OFFSET 0x40000 |

◆ PT5161L_EEPROM_BLOCK_BASE_ADDR

| #define PT5161L_EEPROM_BLOCK_BASE_ADDR 0x88e7 |

◆ PT5161L_EEPROM_BLOCK_CMD_MODIFIER

| #define PT5161L_EEPROM_BLOCK_CMD_MODIFIER 0x80 |

◆ PT5161L_EEPROM_BLOCK_WRITE_SIZE

| #define PT5161L_EEPROM_BLOCK_WRITE_SIZE 32 |

◆ PT5161L_EEPROM_PAGE_SIZE

| #define PT5161L_EEPROM_PAGE_SIZE 256 |

◆ PT5161L_I2C_MST_BB_OUTPUT_ADDRESS

| #define PT5161L_I2C_MST_BB_OUTPUT_ADDRESS 0xd0b |

◆ PT5161L_I2C_MST_CMD_ADDR

| #define PT5161L_I2C_MST_CMD_ADDR 0xd09 |

◆ PT5161L_I2C_MST_DATA0_ADDR

| #define PT5161L_I2C_MST_DATA0_ADDR 0xd05 |

◆ PT5161L_I2C_MST_DATA1_ADDR

| #define PT5161L_I2C_MST_DATA1_ADDR 0xd06 |

◆ PT5161L_I2C_MST_DATA2_ADDR

| #define PT5161L_I2C_MST_DATA2_ADDR 0xd07 |

◆ PT5161L_I2C_MST_DATA3_ADDR

| #define PT5161L_I2C_MST_DATA3_ADDR 0xd08 |

◆ PT5161L_I2C_MST_IC_CMD_ADDR

| #define PT5161L_I2C_MST_IC_CMD_ADDR 0xd04 |

◆ PT5161L_I2C_MST_INIT_CTRL_ADDRESS

| #define PT5161L_I2C_MST_INIT_CTRL_ADDRESS 0xd0a |

◆ PT5161L_I2C_MST_INIT_CTRL_BIT_BANG_MODE_EN_GET

| #define PT5161L_I2C_MST_INIT_CTRL_BIT_BANG_MODE_EN_GET |

( |

|

x | ) |

(((x) & 0x04) >> 2) |

◆ PT5161L_I2C_MST_INIT_CTRL_BIT_BANG_MODE_EN_MODIFY

| #define PT5161L_I2C_MST_INIT_CTRL_BIT_BANG_MODE_EN_MODIFY |

( |

|

r, |

|

|

|

x |

|

) |

| ((((x) << 2) & 0x04) | ((r) & 0xfb)) |

◆ PT5161L_I2C_MST_INIT_CTRL_BIT_BANG_MODE_EN_SET

| #define PT5161L_I2C_MST_INIT_CTRL_BIT_BANG_MODE_EN_SET |

( |

|

x | ) |

(((x) << 2) & 0x04) |

◆ PT5161L_MAIN_MICRO_FW_INFO

| #define PT5161L_MAIN_MICRO_FW_INFO (96 * 1024 - 128) |

◆ PT5161L_MAIN_MICRO_INDIRECT

| #define PT5161L_MAIN_MICRO_INDIRECT 0xd99 |

◆ PT5161L_MAIN_SRAM_DMEM_OFFSET

| #define PT5161L_MAIN_SRAM_DMEM_OFFSET (64 * 1024) |

◆ PT5161L_MM_EEPROM_ASSIST_CMD_ADDR

| #define PT5161L_MM_EEPROM_ASSIST_CMD_ADDR 0x920 |

◆ PT5161L_MM_EEPROM_READ_END_CODE

| #define PT5161L_MM_EEPROM_READ_END_CODE 3 |

◆ PT5161L_MM_EEPROM_READ_REG_CODE

| #define PT5161L_MM_EEPROM_READ_REG_CODE 4 |

◆ PT5161L_MM_EEPROM_WRITE_END_CODE

| #define PT5161L_MM_EEPROM_WRITE_END_CODE 2 |

◆ PT5161L_MM_EEPROM_WRITE_REG_CODE

| #define PT5161L_MM_EEPROM_WRITE_REG_CODE 1 |

◆ PT5161L_MM_FW_VERSION_BUILD

| #define PT5161L_MM_FW_VERSION_BUILD 2 |

◆ PT5161L_MM_FW_VERSION_MAJOR

| #define PT5161L_MM_FW_VERSION_MAJOR 0 |

◆ PT5161L_MM_FW_VERSION_MINOR

| #define PT5161L_MM_FW_VERSION_MINOR 1 |

◆ PT5161L_MM_STATUS_TIME_10MS

| #define PT5161L_MM_STATUS_TIME_10MS 10 |

◆ PT5161L_MM_STATUS_TIME_5MS

| #define PT5161L_MM_STATUS_TIME_5MS 5 |

◆ PT5161L_MUTEX_LOCK_MS

| #define PT5161L_MUTEX_LOCK_MS 1000 |

◆ PT5161L_SELF_WR_CSR_CMD

| #define PT5161L_SELF_WR_CSR_CMD 1 |

◆ PT5161L_TEMP_OFFSET

| #define PT5161L_TEMP_OFFSET 0x42c |

◆ PT5161L_TG_RD_LOC_IND_SRAM

| #define PT5161L_TG_RD_LOC_IND_SRAM 0x16 |

◆ PT5161L_VENDOR_ID_LENGTH

| #define PT5161L_VENDOR_ID_LENGTH 7 |

◆ pcie_retimer_fw_update()

| uint8_t pcie_retimer_fw_update |

( |

I2C_MSG * |

msg, |

|

|

uint32_t |

offset, |

|

|

uint16_t |

msg_len, |

|

|

uint8_t * |

msg_buf, |

|

|

uint8_t |

flag |

|

) |

| |

◆ pt5161l_get_fw_version()

| bool pt5161l_get_fw_version |

( |

I2C_MSG * |

msg, |

|

|

uint8_t * |

version |

|

) |

| |

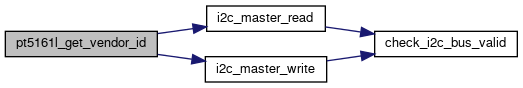

◆ pt5161l_get_vendor_id()

| bool pt5161l_get_vendor_id |

( |

I2C_MSG * |

msg | ) |

|

◆ PT5161L_VENDOR_ID

| uint8_t PT5161L_VENDOR_ID[7] |

|

extern |