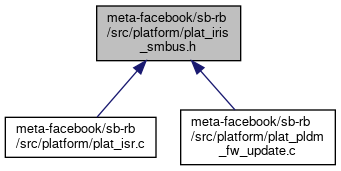

Go to the source code of this file.

◆ ADDR_DATA_LEN_SZ

◆ ADDRESS_BYTE_SZ

| #define ADDRESS_BYTE_SZ 4 |

◆ ASIC_ERROR

◆ BYTE_MASK

◆ BYTES_PER_WORD

◆ CMRT_SIC_MODE

| #define CMRT_SIC_MODE BIT(1) |

◆ DATA_LEN_BYTE_SZ

| #define DATA_LEN_BYTE_SZ 1 |

◆ ERROR_CODE_LEN

◆ FASTBOOT_MODE

| #define FASTBOOT_MODE BIT(0) |

◆ FW_CTRL_READ

◆ FW_CTRL_WRITE

| #define FW_CTRL_WRITE 136 |

◆ FW_DATA_WRITE

| #define FW_DATA_WRITE 138 |

◆ FW_DL_FINISH

| #define FW_DL_FINISH BIT(3) |

◆ FW_DL_HST_ABRT

| #define FW_DL_HST_ABRT BIT(5) |

◆ FW_DL_SLV_ABRTD

| #define FW_DL_SLV_ABRTD BIT(4) |

◆ FW_DL_SLV_DONE

| #define FW_DL_SLV_DONE BIT(2) |

◆ FW_DL_SLV_PROG

| #define FW_DL_SLV_PROG BIT(1) |

◆ FW_DL_SLV_RDY

| #define FW_DL_SLV_RDY BIT(6) |

◆ FW_DL_START

| #define FW_DL_START BIT(7) |

◆ FW_SB_EXIT_CMD

| #define FW_SB_EXIT_CMD BIT(0) |

◆ FW_SMBUS_ERROR

| #define FW_SMBUS_ERROR 130 |

◆ HAMSA_BOOT1_ADDR

| #define HAMSA_BOOT1_ADDR 0x32 |

◆ HAMSA_BOOT1_ASIC_MEM_ADDR

| #define HAMSA_BOOT1_ASIC_MEM_ADDR 0x94008000 |

◆ MAX_DATA_PKT_SIZE

| #define MAX_DATA_PKT_SIZE 24 |

◆ MAX_RETRIES

◆ MEDHA0_I2C_ADDR

| #define MEDHA0_I2C_ADDR 0x33 |

◆ MEDHA1_I2C_ADDR

| #define MEDHA1_I2C_ADDR 0x34 |

◆ MODULE_ERROR

◆ MSG_ADDR_OFFSET

| #define MSG_ADDR_OFFSET 1 |

◆ MSG_DATA_LEN_OFFSET

| #define MSG_DATA_LEN_OFFSET 5 |

◆ MSG_PKT_LEN_OFFSET

| #define MSG_PKT_LEN_OFFSET 0 |

◆ MSG_RDWR_DATA_START

| #define MSG_RDWR_DATA_START 6 |

◆ OWLE_I2C_ADDR

| #define OWLE_I2C_ADDR 0x6E |

◆ OWLW_I2C_ADDR

| #define OWLW_I2C_ADDR 0x6E |

◆ PKT_LEN_BYTE_SZ

| #define PKT_LEN_BYTE_SZ 1 |

◆ RECOVERY_MODE

| #define RECOVERY_MODE BIT(2) |

◆ SB_MODE_QUERY

| #define SB_MODE_QUERY 135 |

◆ SMBUS_ERROR

◆ SMBUS_MAX_PAYLOAD_LEN

| #define SMBUS_MAX_PAYLOAD_LEN 24 |

◆ SMBUS_MAX_PKT_LEN

| #define SMBUS_MAX_PKT_LEN 32 |

◆ STATUS_RETRY_CNT

| #define STATUS_RETRY_CNT 2 |

◆ iris_smbus_fast_boot()

| int iris_smbus_fast_boot |

( |

uint8_t * |

image_buff, |

|

|

uint32_t |

img_dest_addr, |

|

|

uint32_t |

img_size |

|

) |

| |