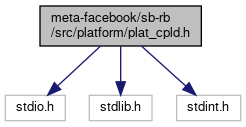

#include <stdio.h>

#include <stdlib.h>

#include <stdint.h>

#include <stdbool.h>

#include <zephyr.h>

Go to the source code of this file.

◆ ASIC_JTAG_MUX_SEL

| #define ASIC_JTAG_MUX_SEL 0x39 |

◆ ASIC_TEMP_OVER_LOG_REG

| #define ASIC_TEMP_OVER_LOG_REG 0x29 |

◆ ASIC_VQPS

◆ ASIC_VR_HOT_SWITCH

| #define ASIC_VR_HOT_SWITCH 0x12 |

◆ CPLD_ADDR

| #define CPLD_ADDR (0x4C >> 1) |

◆ CPLD_ASIC_RESET_STATUS_REG

| #define CPLD_ASIC_RESET_STATUS_REG 0xA2 |

◆ CPLD_HAMSA_PCIE0_PERST_DELAY_REG

| #define CPLD_HAMSA_PCIE0_PERST_DELAY_REG 0x9D |

◆ CPLD_HAMSA_PCIE1_PERST_DELAY_REG

| #define CPLD_HAMSA_PCIE1_PERST_DELAY_REG 0xB3 |

◆ CPLD_HAMSA_PCIE2_PERST_DELAY_REG

| #define CPLD_HAMSA_PCIE2_PERST_DELAY_REG 0xB4 |

◆ CPLD_HAMSA_PCIE3_PERST_DELAY_REG

| #define CPLD_HAMSA_PCIE3_PERST_DELAY_REG 0xB5 |

◆ CPLD_OFFSET_ADC_IDX

| #define CPLD_OFFSET_ADC_IDX 0xA0 |

◆ CPLD_OFFSET_ASIC_BOARD_ID

| #define CPLD_OFFSET_ASIC_BOARD_ID 0x3C |

◆ CPLD_OFFSET_ASIC_RST_DELAY

| #define CPLD_OFFSET_ASIC_RST_DELAY 0xA4 |

◆ CPLD_OFFSET_BOARD_REV_ID

| #define CPLD_OFFSET_BOARD_REV_ID 0x14 |

◆ CPLD_OFFSET_MMC_PWR_EN

| #define CPLD_OFFSET_MMC_PWR_EN 0x38 |

◆ CPLD_OFFSET_MODULE_PG_DELAY

| #define CPLD_OFFSET_MODULE_PG_DELAY 0xA5 |

◆ CPLD_OFFSET_POWER_CAPPING_LV1_TIME

| #define CPLD_OFFSET_POWER_CAPPING_LV1_TIME 0x36 |

◆ CPLD_OFFSET_POWER_CLAMP

| #define CPLD_OFFSET_POWER_CLAMP 0x25 |

◆ CPLD_OFFSET_USERCODE

| #define CPLD_OFFSET_USERCODE 0x32 |

◆ CPLD_OFFSET_VR_VENDER_TYPE

| #define CPLD_OFFSET_VR_VENDER_TYPE 0x15 |

◆ CPLD_POWER_INFO_0_REG

| #define CPLD_POWER_INFO_0_REG 0xB6 |

◆ CPLD_POWER_INFO_1_REG

| #define CPLD_POWER_INFO_1_REG 0xB7 |

◆ HAMSA_MFIO_REG

| #define HAMSA_MFIO_REG 0x17 |

◆ HBM_CATTRIP_LOG_REG

| #define HBM_CATTRIP_LOG_REG 0x27 |

◆ I2C_BUS_CPLD

◆ PREST_DELAY_REG

| #define PREST_DELAY_REG 0x9D |

◆ PWRGD_EVENT_LATCH_1_REG

| #define PWRGD_EVENT_LATCH_1_REG 0xBE |

◆ PWRGD_EVENT_LATCH_2_REG

| #define PWRGD_EVENT_LATCH_2_REG 0xBF |

◆ PWRGD_EVENT_LATCH_3_REG

| #define PWRGD_EVENT_LATCH_3_REG 0xC0 |

◆ PWRGD_EVENT_LATCH_4_REG

| #define PWRGD_EVENT_LATCH_4_REG 0xC1 |

◆ PWRGD_EVENT_LATCH_5_REG

| #define PWRGD_EVENT_LATCH_5_REG 0xC2 |

◆ PWRGD_EVENT_LATCH_6_REG

| #define PWRGD_EVENT_LATCH_6_REG 0xC3 |

◆ RESET

◆ VR_1_EN

◆ VR_1STEP_FUNC_EN_REG

| #define VR_1STEP_FUNC_EN_REG 0xA9 |

◆ VR_2_EN

◆ VR_3_EN

◆ VR_4_EN

◆ VR_AND_CLK_EN

| #define VR_AND_CLK_EN 0x3E |

◆ VR_AND_CLK_EN_PIN_CTRL

| #define VR_AND_CLK_EN_PIN_CTRL 0xA1 |

◆ VR_CLK_ENABLE_PIN_CTRL_REG

| #define VR_CLK_ENABLE_PIN_CTRL_REG 0xA1 |

◆ VR_EN_PIN_READING_5

| #define VR_EN_PIN_READING_5 0x05 |

◆ VR_PWRGD_PIN_READING_1_REG

| #define VR_PWRGD_PIN_READING_1_REG 0x07 |

◆ VR_PWRGD_PIN_READING_2_REG

| #define VR_PWRGD_PIN_READING_2_REG 0x08 |

◆ VR_PWRGD_PIN_READING_3_REG

| #define VR_PWRGD_PIN_READING_3_REG 0x09 |

◆ VR_PWRGD_PIN_READING_4_REG

| #define VR_PWRGD_PIN_READING_4_REG 0x0A |

◆ VR_PWRGD_PIN_READING_5_REG

| #define VR_PWRGD_PIN_READING_5_REG 0x0B |

◆ VR_PWRGD_PIN_READING_6_REG

| #define VR_PWRGD_PIN_READING_6_REG 0x0C |

◆ VR_SMBUS_ALERT_EVENT_LOG_REG

| #define VR_SMBUS_ALERT_EVENT_LOG_REG 0x26 |

◆ cpld_info

◆ check_ubc_delayed()

| void check_ubc_delayed |

( |

struct k_work * |

work | ) |

|

◆ check_ubc_delayed_timer_handler()

| void check_ubc_delayed_timer_handler |

( |

struct k_timer * |

timer | ) |

|

◆ get_cpld_polling_power_info()

| void get_cpld_polling_power_info |

( |

int * |

reading | ) |

|

◆ get_ubc_delaytimer()

| struct k_timer * get_ubc_delaytimer |

( |

| ) |

|

◆ give_all_vr_pm_alert_sem()

| void give_all_vr_pm_alert_sem |

( |

| ) |

|

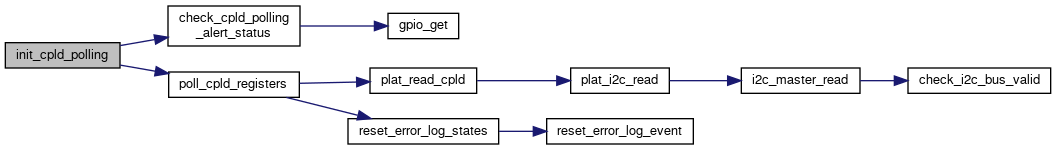

◆ init_cpld_polling()

| void init_cpld_polling |

( |

void |

| ) |

|

◆ is_ubc_enabled_delayed_enabled()

| bool is_ubc_enabled_delayed_enabled |

( |

void |

| ) |

|

◆ plat_read_cpld()

| bool plat_read_cpld |

( |

uint8_t |

offset, |

|

|

uint8_t * |

data, |

|

|

uint8_t |

len |

|

) |

| |

◆ plat_write_cpld()

| bool plat_write_cpld |

( |

uint8_t |

offset, |

|

|

uint8_t * |

data |

|

) |

| |

◆ reset_error_log_states()

| void reset_error_log_states |

( |

uint8_t |

err_type | ) |

|

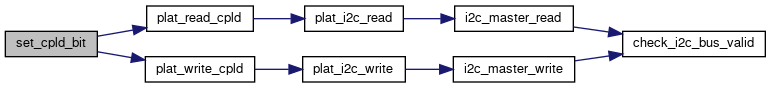

◆ set_cpld_bit()

| bool set_cpld_bit |

( |

uint8_t |

cpld_offset, |

|

|

uint8_t |

bit, |

|

|

uint8_t |

value |

|

) |

| |

◆ set_cpld_polling_enable_flag()

| void set_cpld_polling_enable_flag |

( |

bool |

status | ) |

|