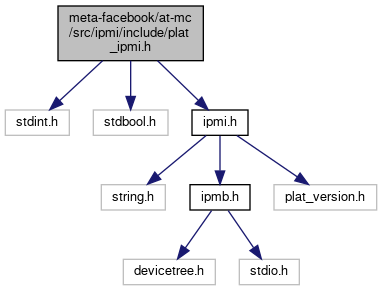

#include <stdint.h>

#include <stdbool.h>

#include "ipmi.h"

Go to the source code of this file.

|

| enum | MC_FIRMWARE_COMPONENT {

MC_COMPNT_BIC = 2

, MC_COMPNT_CPLD = 7

, MC_COMPNT_CXL1 = 16

, MC_COMPNT_CXL2

,

MC_COMPNT_CXL3

, MC_COMPNT_CXL4

, MC_COMPNT_CXL5

, MC_COMPNT_CXL6

,

MC_COMPNT_CXL7

, MC_COMPNT_CXL8

, MC_COMPNT_CXL1_VR_P0V89A

, MC_COMPNT_CXL1_VR_P0V8D_PVDDQ_AB

,

MC_COMPNT_CXL1_VR_VR_PVDDQ_CD

, MC_COMPNT_CXL2_VR_P0V89A

, MC_COMPNT_CXL2_VR_P0V8D_PVDDQ_AB

, MC_COMPNT_CXL2_VR_VR_PVDDQ_CD

,

MC_COMPNT_CXL3_VR_P0V89A

, MC_COMPNT_CXL3_VR_P0V8D_PVDDQ_AB

, MC_COMPNT_CXL3_VR_VR_PVDDQ_CD

, MC_COMPNT_CXL4_VR_P0V89A

,

MC_COMPNT_CXL4_VR_P0V8D_PVDDQ_AB

, MC_COMPNT_CXL4_VR_VR_PVDDQ_CD

, MC_COMPNT_CXL5_VR_P0V89A

, MC_COMPNT_CXL5_VR_P0V8D_PVDDQ_AB

,

MC_COMPNT_CXL5_VR_VR_PVDDQ_CD

, MC_COMPNT_CXL6_VR_P0V89A

, MC_COMPNT_CXL6_VR_P0V8D_PVDDQ_AB

, MC_COMPNT_CXL6_VR_VR_PVDDQ_CD

,

MC_COMPNT_CXL7_VR_P0V89A

, MC_COMPNT_CXL7_VR_P0V8D_PVDDQ_AB

, MC_COMPNT_CXL7_VR_VR_PVDDQ_CD

, MC_COMPNT_CXL8_VR_P0V89A

,

MC_COMPNT_CXL8_VR_P0V8D_PVDDQ_AB

, MC_COMPNT_CXL8_VR_VR_PVDDQ_CD

, MC_COMPNT_MAX

} |

| |

| enum | CXL_FRU_OPTIONAL { CXL_FRU_WRITE

, CXL_FRU_READ

} |

| |

◆ BIC_FW_DATA_LENGTH

| #define BIC_FW_DATA_LENGTH 7 |

◆ BIC_UPDATE_MAX_OFFSET

| #define BIC_UPDATE_MAX_OFFSET 0x50000 |

◆ IS_SECTOR_END_MASK

| #define IS_SECTOR_END_MASK 0x80 |

◆ PCIE_CARD_DEVICE_NOT_READY_BIT

| #define PCIE_CARD_DEVICE_NOT_READY_BIT BIT(2) |

◆ PCIE_CARD_ID_OFFSET

| #define PCIE_CARD_ID_OFFSET 30 |

◆ PCIE_CARD_NOT_ACCESSIABLE_BIT

| #define PCIE_CARD_NOT_ACCESSIABLE_BIT BIT(1) |

◆ PCIE_CARD_NOT_PRESENT

| #define PCIE_CARD_NOT_PRESENT 0 |

◆ PCIE_CARD_NOT_PRESENT_BIT

| #define PCIE_CARD_NOT_PRESENT_BIT BIT(0) |

◆ PCIE_CARD_PRESENT

| #define PCIE_CARD_PRESENT 1 |

◆ PM8702_BUSY_DELAY_MS

| #define PM8702_BUSY_DELAY_MS 100 |

◆ PM8702_DEFAULT_NEXT_ACTIVE_SLOT

| #define PM8702_DEFAULT_NEXT_ACTIVE_SLOT 0 |

◆ PM8702_INITIATE_FW_OFFSET

| #define PM8702_INITIATE_FW_OFFSET 0x0000 |

◆ PM8702_NO_HBO_RUN_VAL

| #define PM8702_NO_HBO_RUN_VAL 0 |

◆ PM8702_RETURN_SUCCESS

| #define PM8702_RETURN_SUCCESS 0x00 |

◆ PM8702_TRANSFER_DELAY_MS

| #define PM8702_TRANSFER_DELAY_MS 20 |

◆ PM8702_TRANSFER_FW_DATA_LEN

| #define PM8702_TRANSFER_FW_DATA_LEN 128 |

◆ PM8702_TRANSFER_FW_HEADER_LEN

| #define PM8702_TRANSFER_FW_HEADER_LEN 128 |

◆ PM8702_UPDATE_MAX_OFFSET

| #define PM8702_UPDATE_MAX_OFFSET 0x150000 |

◆ WITHOUT_SENCTOR_END_MASK

| #define WITHOUT_SENCTOR_END_MASK 0x7F |

◆ CXL_FRU_OPTIONAL

| Enumerator |

|---|

| CXL_FRU_WRITE | |

| CXL_FRU_READ | |

◆ MC_FIRMWARE_COMPONENT

enum number follow GT for now since bmc hasn't ready

| Enumerator |

|---|

| MC_COMPNT_BIC | |

| MC_COMPNT_CPLD | |

| MC_COMPNT_CXL1 | |

| MC_COMPNT_CXL2 | |

| MC_COMPNT_CXL3 | |

| MC_COMPNT_CXL4 | |

| MC_COMPNT_CXL5 | |

| MC_COMPNT_CXL6 | |

| MC_COMPNT_CXL7 | |

| MC_COMPNT_CXL8 | |

| MC_COMPNT_CXL1_VR_P0V89A | |

| MC_COMPNT_CXL1_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL1_VR_VR_PVDDQ_CD | |

| MC_COMPNT_CXL2_VR_P0V89A | |

| MC_COMPNT_CXL2_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL2_VR_VR_PVDDQ_CD | |

| MC_COMPNT_CXL3_VR_P0V89A | |

| MC_COMPNT_CXL3_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL3_VR_VR_PVDDQ_CD | |

| MC_COMPNT_CXL4_VR_P0V89A | |

| MC_COMPNT_CXL4_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL4_VR_VR_PVDDQ_CD | |

| MC_COMPNT_CXL5_VR_P0V89A | |

| MC_COMPNT_CXL5_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL5_VR_VR_PVDDQ_CD | |

| MC_COMPNT_CXL6_VR_P0V89A | |

| MC_COMPNT_CXL6_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL6_VR_VR_PVDDQ_CD | |

| MC_COMPNT_CXL7_VR_P0V89A | |

| MC_COMPNT_CXL7_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL7_VR_VR_PVDDQ_CD | |

| MC_COMPNT_CXL8_VR_P0V89A | |

| MC_COMPNT_CXL8_VR_P0V8D_PVDDQ_AB | |

| MC_COMPNT_CXL8_VR_VR_PVDDQ_CD | |

| MC_COMPNT_MAX | |

◆ pal_construct_ipmi_add_sel_msg()