#include <stdio.h>#include <stdlib.h>#include <drivers/sensor.h>#include <drivers/pwm.h>#include <logging/log.h>#include "sensor.h"#include "pmbus.h"#include "libutil.h"#include "hal_i2c.h"#include "plat_dev.h"#include "plat_hook.h"#include "plat_class.h"#include "common_i2c_mux.h"#include "plat_sensor_table.h"#include "nvme.h"#include "plat_ipmi.h"#include "util_worker.h"#include "pex89000.h"#include "pldm_monitor.h"#include "plat_pldm_monitor.h"#include "xdpe15284.h"#include "util_pmbus.h"#include "plat_isr.h"#include "pldm_state_set.h"

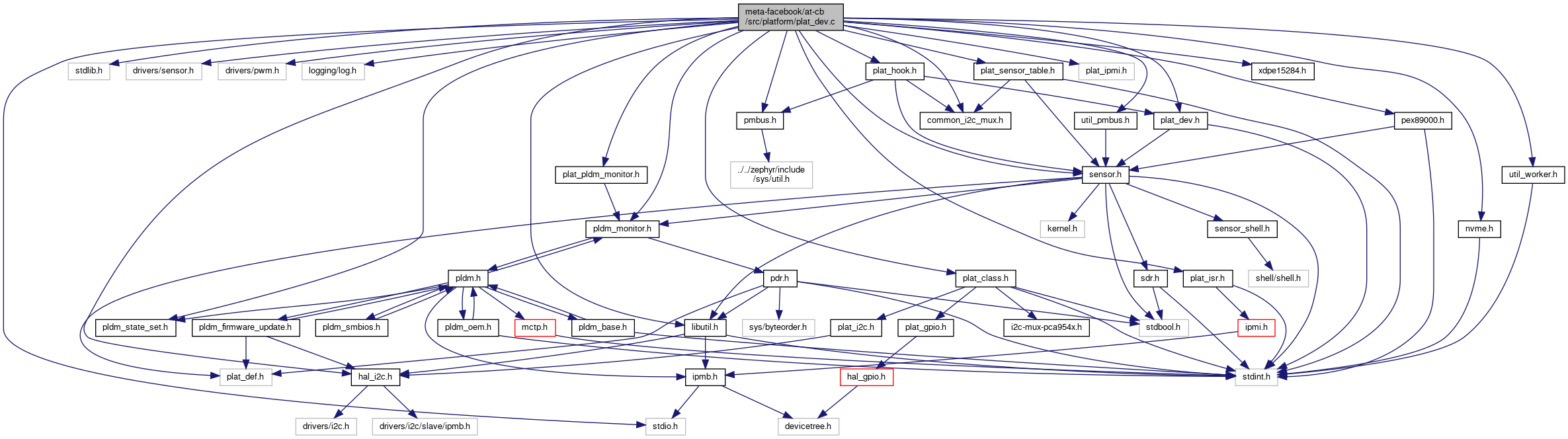

Include dependency graph for plat_dev.c:

Classes | |

| struct | _hbin_header |

| struct | _payload_header |

| struct | _sb_cmd_fw_update |

| struct | _sw_error_event_cfg |

Typedefs | |

| typedef struct _hbin_header | hbin_header |

| typedef struct _payload_header | payload_header |

| typedef struct _sw_error_event_cfg | sw_error_event_cfg |

Enumerations | |

| enum | ATM_FW_UPDATE_REG_OFFSET { SB_CMD_FW_SMBUS_ERROR_CODE = 0x82 , SB_CMD_FW_UPDATE = 0x84 , SB_CMD_FW_UPDATE_CONTROL = 0x85 , SB_CMD_FW_UPDATE_EXT = 0x87 , SB_CMD_FW_UPDATE_ERROR_CODE = 0x94 , TRANSFER_MEM_START = 0xA4 , LCS_STATE = 0xBF , TRANSFER_HEADER_PAGE = 0xC1 , TRANSFER_DATA_PACKET = 0xC7 , SB_PAYLOAD_EXEC_T = 0xE9 } |

| enum | ATM_SB_CMD_FW_UPDATE_BIT { SB_CMD_FW_UPDATE_IN_PROGRESS_BIT = BIT(1) , SB_CMD_FW_UPDATE_UPDATE_COMPLETE_BIT = BIT(2) , SB_CMD_FW_UPDATE_TRANSFER_DONE_BIT = BIT(3) , SB_CMD_FW_UPDATE_TRANSFER_READY_BIT = BIT(6) , SB_CMD_FW_UPDATE_INITIATE_DOWNLOAD_BIT = BIT(7) } |

Functions | |

| LOG_MODULE_REGISTER (plat_dev) | |

| K_THREAD_STACK_DEFINE (sw_heartbeat_thread, SW_HEARTBEAT_STACK_SIZE) | |

| struct _sb_cmd_fw_update | __attribute__ ((__packed__)) |

| void | clear_freya_cache_flag (uint8_t card_id) |

| void | clear_accl_cable_power_fault_flag () |

| int | get_freya_fw_info (uint8_t bus, uint8_t addr, freya_fw_info *fw_info) |

| bool | get_pex_heartbeat (char *label) |

| void | sw_heartbeat_read () |

| void | init_sw_heartbeat_thread () |

| bool | is_sw_ready (uint8_t sensor_num) |

| void | init_sw_heartbeat_work () |

| void | clear_sw_error_check_flag () |

| void | sw_error_event_handler (struct k_work *work_item) |

| void | get_switch_error_status (uint8_t sensor_num, uint8_t bus, uint8_t addr, uint8_t index) |

| bool | init_vr_write_protect (uint8_t bus, uint8_t addr, uint8_t default_val) |

| int | check_error_status (uint8_t bus, uint8_t addr, uint32_t *error_code, uint8_t *smbus_error_code) |

| int | get_boot1_complete_bit (uint8_t bus, uint8_t addr, uint8_t *bit) |

| int | sb_cmd_fw_update_bit_operation (uint8_t bus, uint8_t addr, uint8_t optional, uint8_t bit_value) |

| int | check_fw_update_bit_operation (uint8_t bus, uint8_t addr, uint8_t optional, uint8_t bit_value) |

| int | get_atm_transfer_info (uint8_t bus, uint8_t addr, uint32_t *transfer_mem_start, uint32_t *transfer_mem_size) |

| int | pre_atm_fw_update_check (uint8_t *msg_buf, uint16_t buf_len, hbin_header *h_header, payload_header *p_header) |

| int | check_is_fw_abort_update (uint8_t bus, uint8_t addr, uint32_t *error_code, uint8_t *smbus_error_code) |

| int | wait_for_fw_ready (uint8_t bus, uint8_t addr, uint8_t bit_value, uint8_t timeout_s) |

| int | init_fw_update_setting (uint8_t bus, uint8_t addr, uint32_t image_size, uint32_t transfer_addr) |

| int | check_exec_status (uint8_t bus, uint8_t addr, uint8_t *status, uint8_t *result) |

| void | wait_firmware_work_handler (struct k_work *work_item) |

| int | transfer_data (uint8_t bus, uint8_t addr, uint32_t offset, uint8_t *msg_buf, uint16_t buf_len) |

| int | atm_fw_update (uint8_t bus, uint8_t addr, uint32_t offset, uint8_t *msg_buf, uint16_t buf_len, uint32_t image_size, bool is_end_package) |

| void | init_clk_gen_spread_spectrum_control_register () |

Variables | |

| struct k_thread | sw_heartbeat_thread_handler |

| k_tid_t | sw_heartbeat_tid |

| uint8_t | length |

| uint8_t | control_option |

| uint8_t | pec |

| freya_info | accl_freya_info [] |

| vr_fw_info | cb_vr_fw_info = { .is_init = false } |

| switch_error_check_info | sw_error_check_info [] |

Macro Definition Documentation

◆ BLOCK_DATA_COUNT

| #define BLOCK_DATA_COUNT 32 |

◆ BOOT1_COMPLETE_BIT

| #define BOOT1_COMPLETE_BIT BIT(7) |

◆ CHECK_IS_PROGRESS_DELAY_MS

| #define CHECK_IS_PROGRESS_DELAY_MS 1000 |

◆ CLK_GEN_SSC_HW_EXPECT_VALUE

| #define CLK_GEN_SSC_HW_EXPECT_VALUE 0x02 |

◆ ERROR_CODE_REG_LEN

| #define ERROR_CODE_REG_LEN 4 |

◆ FW_ABORT_UPDATE_RETURN_VAL

| #define FW_ABORT_UPDATE_RETURN_VAL -2 |

◆ FW_EXEC_STATUS_RUNNING_RETURN_VAL

| #define FW_EXEC_STATUS_RUNNING_RETURN_VAL 1 |

◆ FW_READY_WAIT_TIMEOUT_RETURN_VAL

| #define FW_READY_WAIT_TIMEOUT_RETURN_VAL -2 |

◆ FW_UPDATE_COMMAND_DEFAULT_VAL

| #define FW_UPDATE_COMMAND_DEFAULT_VAL 0x01 |

◆ HBIN_HEADER_SIZE

| #define HBIN_HEADER_SIZE 0x30 |

◆ HBIN_HEADER_UID

| #define HBIN_HEADER_UID 0x36148967 |

◆ HBIN_HEADER_VER

| #define HBIN_HEADER_VER 0x03 |

◆ INVALID_FW_DATA

| #define INVALID_FW_DATA 0xFF |

◆ PAYLOAD_HEADER_SIZE

| #define PAYLOAD_HEADER_SIZE 0x10 |

◆ PAYLOAD_HEADER_TYPE_BOOT1

| #define PAYLOAD_HEADER_TYPE_BOOT1 0x01 |

◆ PAYLOAD_HEADER_TYPE_PSOC

| #define PAYLOAD_HEADER_TYPE_PSOC 0x1C |

◆ PAYLOAD_HEADER_TYPE_QSPI

| #define PAYLOAD_HEADER_TYPE_QSPI 0x16 |

◆ PAYLOAD_HEADER_UID1

| #define PAYLOAD_HEADER_UID1 0x1D436F81 |

◆ PAYLOAD_HEADER_UID2

| #define PAYLOAD_HEADER_UID2 0xE2BC907E |

◆ PAYLOAD_HEADER_VER

| #define PAYLOAD_HEADER_VER 0x02 |

◆ PSOC_QSPI_FW_INDEX

| #define PSOC_QSPI_FW_INDEX (FREYA_FIRMWARE_VERSION_OFFSET + 2) |

◆ SOC_QSPI_FW_LENGTH

| #define SOC_QSPI_FW_LENGTH 3 |

◆ SW_HEARTBEAT_DELAY_MS

| #define SW_HEARTBEAT_DELAY_MS 2000 |

◆ SW_HEARTBEAT_STACK_SIZE

| #define SW_HEARTBEAT_STACK_SIZE 1024 |

◆ TARGET_DEST_DEFAULT_VAL

| #define TARGET_DEST_DEFAULT_VAL 0x01 |

◆ TARGET_SRC_DEFAULT_VAL

| #define TARGET_SRC_DEFAULT_VAL 0x00 |

◆ TRANSFER_MEM_INFO_LEN

| #define TRANSFER_MEM_INFO_LEN 8 |

◆ UNEXPECTED_FW_DATA

| #define UNEXPECTED_FW_DATA 0x00 |

◆ WAIT_BOOT1_FIRMWARE_UPDATE_COMPLETE_TIMEOUT_S

| #define WAIT_BOOT1_FIRMWARE_UPDATE_COMPLETE_TIMEOUT_S 20 |

◆ WAIT_FIRMWARE_READY_DELAY_TIMEOUT_S

| #define WAIT_FIRMWARE_READY_DELAY_TIMEOUT_S 5 |

◆ WAIT_PSOC_FIRMWARE_UPDATE_COMPLETE_TIMEOUT_S

| #define WAIT_PSOC_FIRMWARE_UPDATE_COMPLETE_TIMEOUT_S 60 |

◆ WAIT_QSPI_FIRMWARE_UPDATE_COMPLETE_TIMEOUT_S

| #define WAIT_QSPI_FIRMWARE_UPDATE_COMPLETE_TIMEOUT_S 15 |

Typedef Documentation

◆ hbin_header

| typedef struct _hbin_header hbin_header |

◆ payload_header

| typedef struct _payload_header payload_header |

◆ sw_error_event_cfg

| typedef struct _sw_error_event_cfg sw_error_event_cfg |

Enumeration Type Documentation

◆ ATM_FW_UPDATE_REG_OFFSET

◆ ATM_SB_CMD_FW_UPDATE_BIT

Function Documentation

◆ __attribute__()

| struct _sb_cmd_fw_update __attribute__ | ( | (__packed__) | ) |

◆ atm_fw_update()

| int atm_fw_update | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint32_t | offset, | ||

| uint8_t * | msg_buf, | ||

| uint16_t | buf_len, | ||

| uint32_t | image_size, | ||

| bool | is_end_package | ||

| ) |

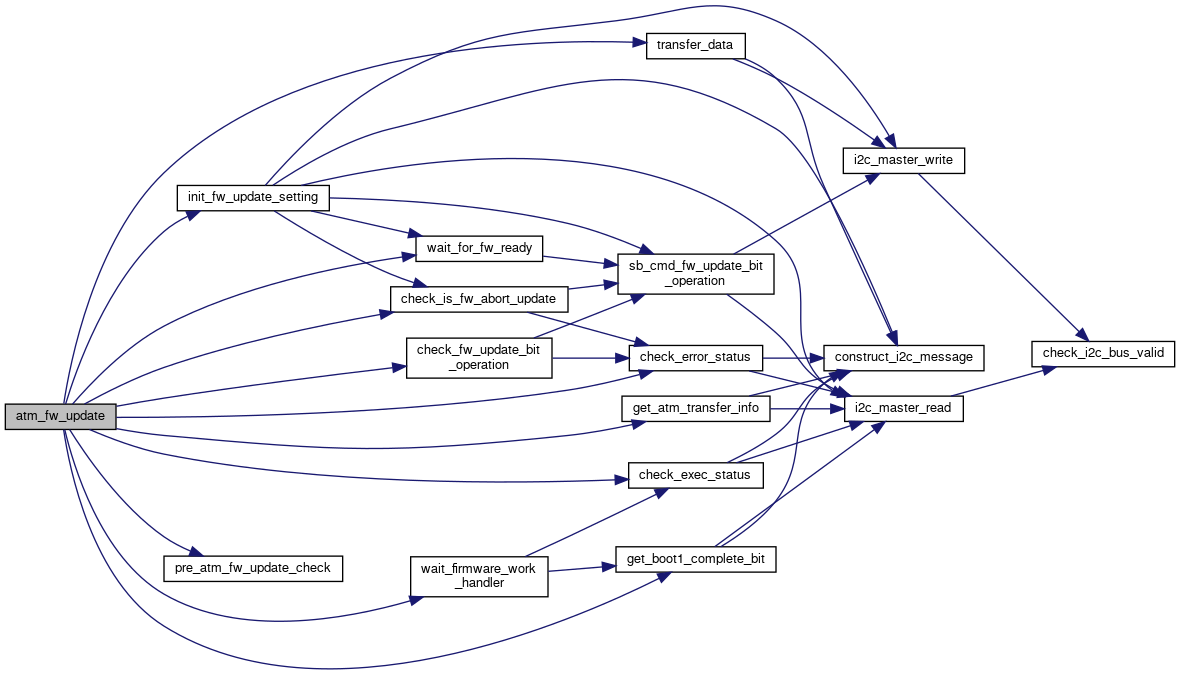

Here is the call graph for this function:

◆ check_error_status()

| int check_error_status | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint32_t * | error_code, | ||

| uint8_t * | smbus_error_code | ||

| ) |

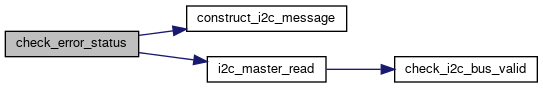

Here is the call graph for this function:

◆ check_exec_status()

| int check_exec_status | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint8_t * | status, | ||

| uint8_t * | result | ||

| ) |

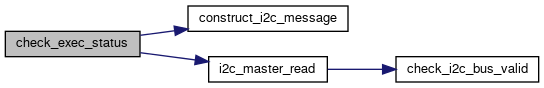

Here is the call graph for this function:

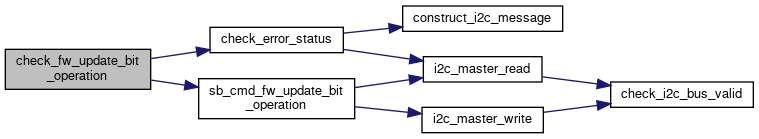

◆ check_fw_update_bit_operation()

| int check_fw_update_bit_operation | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint8_t | optional, | ||

| uint8_t | bit_value | ||

| ) |

Here is the call graph for this function:

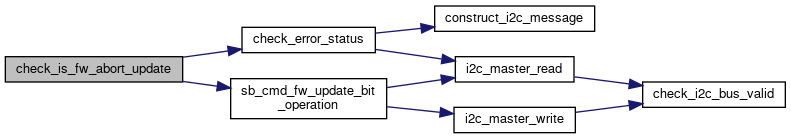

◆ check_is_fw_abort_update()

| int check_is_fw_abort_update | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint32_t * | error_code, | ||

| uint8_t * | smbus_error_code | ||

| ) |

Here is the call graph for this function:

◆ clear_accl_cable_power_fault_flag()

| void clear_accl_cable_power_fault_flag | ( | ) |

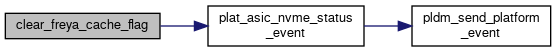

◆ clear_freya_cache_flag()

| void clear_freya_cache_flag | ( | uint8_t | card_id | ) |

Here is the call graph for this function:

◆ clear_sw_error_check_flag()

| void clear_sw_error_check_flag | ( | ) |

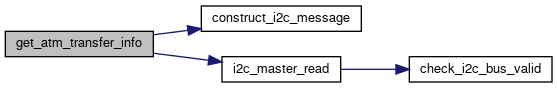

◆ get_atm_transfer_info()

| int get_atm_transfer_info | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint32_t * | transfer_mem_start, | ||

| uint32_t * | transfer_mem_size | ||

| ) |

Here is the call graph for this function:

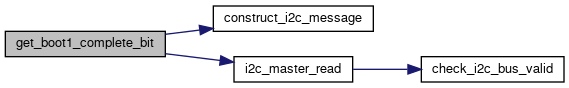

◆ get_boot1_complete_bit()

| int get_boot1_complete_bit | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint8_t * | bit | ||

| ) |

Here is the call graph for this function:

◆ get_freya_fw_info()

| int get_freya_fw_info | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| freya_fw_info * | fw_info | ||

| ) |

Here is the call graph for this function:

◆ get_pex_heartbeat()

| bool get_pex_heartbeat | ( | char * | label | ) |

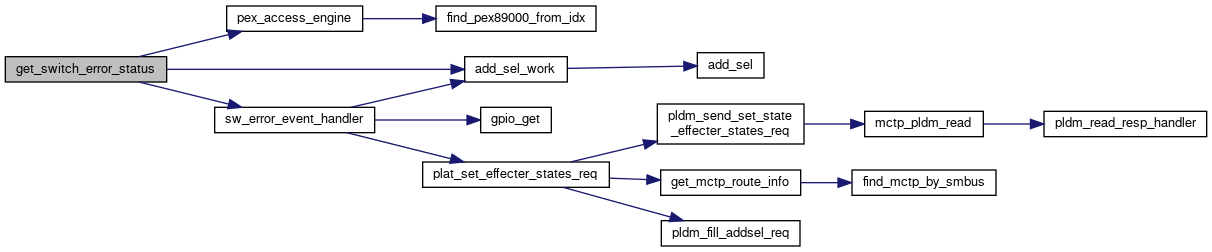

◆ get_switch_error_status()

| void get_switch_error_status | ( | uint8_t | sensor_num, |

| uint8_t | bus, | ||

| uint8_t | addr, | ||

| uint8_t | index | ||

| ) |

Here is the call graph for this function:

◆ init_clk_gen_spread_spectrum_control_register()

| void init_clk_gen_spread_spectrum_control_register | ( | ) |

Here is the call graph for this function:

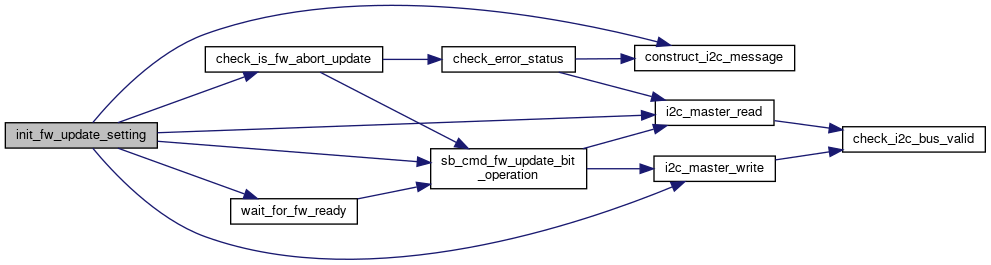

◆ init_fw_update_setting()

| int init_fw_update_setting | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint32_t | image_size, | ||

| uint32_t | transfer_addr | ||

| ) |

Here is the call graph for this function:

◆ init_sw_heartbeat_thread()

| void init_sw_heartbeat_thread | ( | ) |

Here is the call graph for this function:

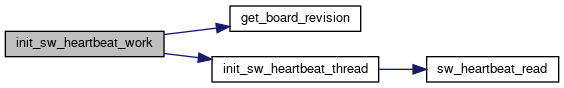

◆ init_sw_heartbeat_work()

| void init_sw_heartbeat_work | ( | ) |

Here is the call graph for this function:

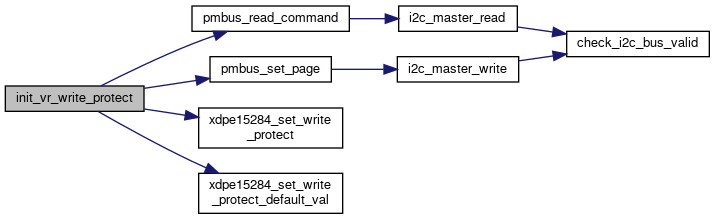

◆ init_vr_write_protect()

| bool init_vr_write_protect | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint8_t | default_val | ||

| ) |

Here is the call graph for this function:

◆ is_sw_ready()

| bool is_sw_ready | ( | uint8_t | sensor_num | ) |

◆ K_THREAD_STACK_DEFINE()

| K_THREAD_STACK_DEFINE | ( | sw_heartbeat_thread | , |

| SW_HEARTBEAT_STACK_SIZE | |||

| ) |

◆ LOG_MODULE_REGISTER()

| LOG_MODULE_REGISTER | ( | plat_dev | ) |

◆ pre_atm_fw_update_check()

| int pre_atm_fw_update_check | ( | uint8_t * | msg_buf, |

| uint16_t | buf_len, | ||

| hbin_header * | h_header, | ||

| payload_header * | p_header | ||

| ) |

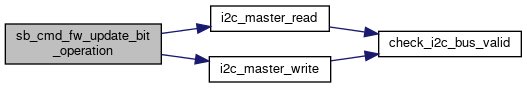

◆ sb_cmd_fw_update_bit_operation()

| int sb_cmd_fw_update_bit_operation | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint8_t | optional, | ||

| uint8_t | bit_value | ||

| ) |

Here is the call graph for this function:

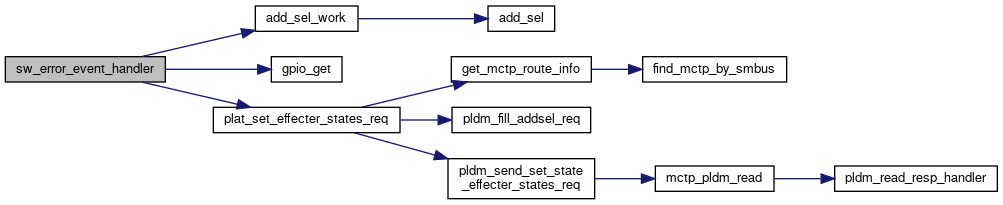

◆ sw_error_event_handler()

| void sw_error_event_handler | ( | struct k_work * | work_item | ) |

Here is the call graph for this function:

◆ sw_heartbeat_read()

| void sw_heartbeat_read | ( | ) |

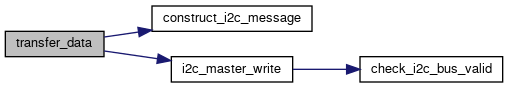

◆ transfer_data()

| int transfer_data | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint32_t | offset, | ||

| uint8_t * | msg_buf, | ||

| uint16_t | buf_len | ||

| ) |

Here is the call graph for this function:

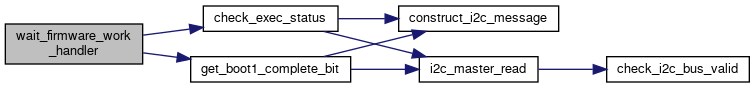

◆ wait_firmware_work_handler()

| void wait_firmware_work_handler | ( | struct k_work * | work_item | ) |

Here is the call graph for this function:

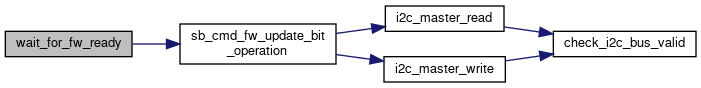

◆ wait_for_fw_ready()

| int wait_for_fw_ready | ( | uint8_t | bus, |

| uint8_t | addr, | ||

| uint8_t | bit_value, | ||

| uint8_t | timeout_s | ||

| ) |

Here is the call graph for this function:

Variable Documentation

◆ accl_freya_info

| freya_info accl_freya_info[] |

Initial value:

= {

[0] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[1] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[2] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[3] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[4] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[5] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[6] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[7] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[8] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[9] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[10] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

[11] = { .is_cache_freya1_info = false, .is_cache_freya2_info = false },

}

◆ cb_vr_fw_info

| vr_fw_info cb_vr_fw_info = { .is_init = false } |

◆ control_option

| uint8_t control_option |

◆ length

| uint8_t length |

◆ pec

| uint8_t pec |

◆ sw_error_check_info

| switch_error_check_info sw_error_check_info[] |

Initial value:

= {

{ .is_addsel = false,

.is_init_work = false,

.device_type = PLDM_ADDSEL_DEVICE_TYPE_PEX_SWITCH_0 },

{ .is_addsel = false,

.is_init_work = false,

.device_type = PLDM_ADDSEL_DEVICE_TYPE_PEX_SWITCH_1 },

}

@ PLDM_ADDSEL_DEVICE_TYPE_PEX_SWITCH_0

Definition: plat_pldm_monitor.h:101

@ PLDM_ADDSEL_DEVICE_TYPE_PEX_SWITCH_1

Definition: plat_pldm_monitor.h:102

◆ sw_heartbeat_thread_handler

| struct k_thread sw_heartbeat_thread_handler |

◆ sw_heartbeat_tid

| k_tid_t sw_heartbeat_tid |