#include <shell/shell.h>#include <stdlib.h>#include <string.h>#include <logging/log.h>#include "plat_cpld.h"

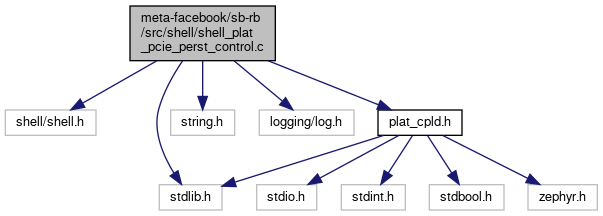

Include dependency graph for shell_plat_pcie_perst_control.c:

Macros | |

| #define | PCIE_PERST_CPLD_OFFSET 0xA3 |

| #define | PCIE_PERST_OVERRIDE_ON 0xFF |

| #define | PCIE_PERST_OVERRIDE_OFF 0xF0 |

| #define | HAMSA_PCIE0_PERST_BIT 0 |

| #define | HAMSA_PCIE1_PERST_BIT 1 |

| #define | HAMSA_PCIE2_PERST_BIT 2 |

| #define | HAMSA_PCIE3_PERST_BIT 3 |

Functions | |

| LOG_MODULE_REGISTER (pcie_perst_control, LOG_LEVEL_DBG) | |

| SHELL_STATIC_SUBCMD_SET_CREATE (pcie_perst_subcmds, SHELL_CMD(override, NULL, "pcie_perst_control override <0|1>", cmd_pcie_perst_override), SHELL_CMD(get, NULL, "pcie_perst_control get all | get <NAME>", cmd_pcie_perst_get), SHELL_CMD(set, NULL, "pcie_perst_control set <NAME> <0|1>", cmd_pcie_perst_set), SHELL_SUBCMD_SET_END) | |

| SHELL_CMD_REGISTER (pcie_perst_control, &pcie_perst_subcmds, "PCIe PERST control via CPLD", NULL) | |

Macro Definition Documentation

◆ HAMSA_PCIE0_PERST_BIT

| #define HAMSA_PCIE0_PERST_BIT 0 |

◆ HAMSA_PCIE1_PERST_BIT

| #define HAMSA_PCIE1_PERST_BIT 1 |

◆ HAMSA_PCIE2_PERST_BIT

| #define HAMSA_PCIE2_PERST_BIT 2 |

◆ HAMSA_PCIE3_PERST_BIT

| #define HAMSA_PCIE3_PERST_BIT 3 |

◆ PCIE_PERST_CPLD_OFFSET

| #define PCIE_PERST_CPLD_OFFSET 0xA3 |

◆ PCIE_PERST_OVERRIDE_OFF

| #define PCIE_PERST_OVERRIDE_OFF 0xF0 |

◆ PCIE_PERST_OVERRIDE_ON

| #define PCIE_PERST_OVERRIDE_ON 0xFF |

Function Documentation

◆ LOG_MODULE_REGISTER()

| LOG_MODULE_REGISTER | ( | pcie_perst_control | , |

| LOG_LEVEL_DBG | |||

| ) |

◆ SHELL_CMD_REGISTER()

| SHELL_CMD_REGISTER | ( | pcie_perst_control | , |

| & | pcie_perst_subcmds, | ||

| "PCIe PERST control via CPLD" | , | ||

| NULL | |||

| ) |

◆ SHELL_STATIC_SUBCMD_SET_CREATE()

| SHELL_STATIC_SUBCMD_SET_CREATE | ( | pcie_perst_subcmds | , |

| SHELL_CMD(override, NULL, "pcie_perst_control override <0|1>", cmd_pcie_perst_override) | , | ||

| SHELL_CMD(get, NULL, "pcie_perst_control get all | get <NAME>", cmd_pcie_perst_get) | , | ||

| SHELL_CMD(set, NULL, "pcie_perst_control set <NAME> <0|1>", cmd_pcie_perst_set) | , | ||

| SHELL_SUBCMD_SET_END | |||

| ) |