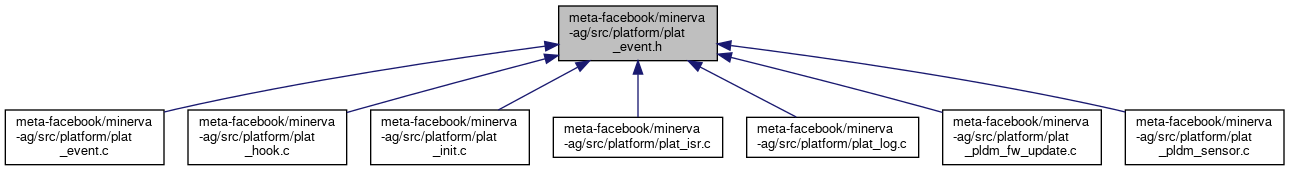

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | _aegis_cpld_info_ |

| struct | cpld_bit_name_table_t |

Typedefs | |

| typedef struct _aegis_cpld_info_ | aegis_cpld_info |

Functions | |

| void | check_ubc_delayed_timer_handler (struct k_timer *timer) |

| void | check_ubc_delayed (struct k_work *work) |

| void | plat_set_ac_on_log () |

| void | plat_set_dc_on_log (bool is_assert) |

| void | plat_set_power_down_log () |

| void | check_cpld_polling_alert_status () |

| void | set_cpld_polling_enable_flag (bool status) |

| bool | get_cpld_polling_enable_flag (void) |

| void | init_cpld_polling (void) |

| bool | is_ubc_enabled_delayed_enabled (void) |

| void | set_ubc_enabled_delayed_enabled (bool status) |

| void | cancel_ubc_delayed_timer_handler (void) |

| const char * | get_cpld_reg_name (uint8_t cpld_offset) |

| const char * | get_cpld_bit_name (uint8_t cpld_offset, uint8_t bit_pos) |

Macro Definition Documentation

◆ AEGIS_JTAG_SWITCH_REG

| #define AEGIS_JTAG_SWITCH_REG 0x20 |

◆ ASIC_OC_WARN_2_REG

| #define ASIC_OC_WARN_2_REG 0x98 |

◆ ASIC_OC_WARN_REG

| #define ASIC_OC_WARN_REG 0x27 |

◆ ATH_BOOT_SOURCE_REG

| #define ATH_BOOT_SOURCE_REG 0x21 |

◆ ATH_JTAG_SEL_MUX_REG

| #define ATH_JTAG_SEL_MUX_REG 0x1E |

◆ ATH_RSVD_GPIO_REG

| #define ATH_RSVD_GPIO_REG 0x3C |

◆ BOARD_REV_ID_REG

| #define BOARD_REV_ID_REG 0x1B |

◆ BOARD_TYPE_REG

| #define BOARD_TYPE_REG 0x1A |

◆ BUFFER_100M_CLK_LOSE_OF_INPUT_SIGNAL_REG

| #define BUFFER_100M_CLK_LOSE_OF_INPUT_SIGNAL_REG 0x3A |

◆ CMN_STATUS_REG

| #define CMN_STATUS_REG 0x31 |

◆ CPLD_EEPROM_STATUS_REG

| #define CPLD_EEPROM_STATUS_REG 0x35 |

◆ CRD_STATUS_REG

| #define CRD_STATUS_REG 0x30 |

◆ FM_AEGIS_CLK_100MHZ_EN_N_OFF_REG

| #define FM_AEGIS_CLK_100MHZ_EN_N_OFF_REG 0x74 |

◆ FM_AEGIS_CLK_100MHZ_EN_N_ON_REG

| #define FM_AEGIS_CLK_100MHZ_EN_N_ON_REG 0x65 |

◆ FM_AEGIS_CLK_312MHZ_EN_OFF_REG

| #define FM_AEGIS_CLK_312MHZ_EN_OFF_REG 0x75 |

◆ FM_AEGIS_CLK_312MHZ_EN_ON_REG

| #define FM_AEGIS_CLK_312MHZ_EN_ON_REG 0x66 |

◆ FM_AEGIS_CLK_48MHZ_EN_OFF_REG

| #define FM_AEGIS_CLK_48MHZ_EN_OFF_REG 0x73 |

◆ FM_AEGIS_CLK_48MHZ_EN_ON_REG

| #define FM_AEGIS_CLK_48MHZ_EN_ON_REG 0x64 |

◆ LEAK_DETCTION_REG

| #define LEAK_DETCTION_REG 0x2E |

◆ MB_POWER_GOOD_AND_PERST_PIN_READING_REG

| #define MB_POWER_GOOD_AND_PERST_PIN_READING_REG 0x06 |

◆ MTIA_ATH_TEST_PIN_STATUS_REG

| #define MTIA_ATH_TEST_PIN_STATUS_REG 0x38 |

◆ MTIA_N_OWL_TEST_PIN_STATUS_REG

| #define MTIA_N_OWL_TEST_PIN_STATUS_REG 0x36 |

◆ MTIA_QSPI_BOOT_DISABLE_REG

| #define MTIA_QSPI_BOOT_DISABLE_REG 0x3B |

◆ MTIA_S_OWL_TEST_PIN_STATUS_REG

| #define MTIA_S_OWL_TEST_PIN_STATUS_REG 0x37 |

◆ MTIA_VQPS_TO_EFUSE_PROGRAMMING_REG

| #define MTIA_VQPS_TO_EFUSE_PROGRAMMING_REG 0x39 |

◆ N_OWL_BOOT_SOURCE_REG

| #define N_OWL_BOOT_SOURCE_REG 0x23 |

◆ OSFP_POWER_ENABLE_PIN_READING_1_REG

| #define OSFP_POWER_ENABLE_PIN_READING_1_REG 0x16 |

◆ OSFP_POWER_ENABLE_PIN_READING_2_REG

| #define OSFP_POWER_ENABLE_PIN_READING_2_REG 0x17 |

◆ OSFP_POWER_ENABLE_PIN_READING_3_REG

| #define OSFP_POWER_ENABLE_PIN_READING_3_REG 0x18 |

◆ OSFP_POWER_ENABLE_PIN_READING_4_REG

| #define OSFP_POWER_ENABLE_PIN_READING_4_REG 0x19 |

◆ OSFP_PRSNT_PIN_READING_1_REG

| #define OSFP_PRSNT_PIN_READING_1_REG 0x14 |

◆ OSFP_PRSNT_PIN_READING_2_REG

| #define OSFP_PRSNT_PIN_READING_2_REG 0x15 |

◆ OWL_JTAG_SEL_MUX_REG

| #define OWL_JTAG_SEL_MUX_REG 0x1D |

◆ OWL_UART_SEL_MUX_REG

| #define OWL_UART_SEL_MUX_REG 0x1F |

◆ P12V_UBC_PWRGD_OFF_REG

| #define P12V_UBC_PWRGD_OFF_REG 0x96 |

◆ P12V_UBC_PWRGD_ON_REG

| #define P12V_UBC_PWRGD_ON_REG 0x48 |

◆ POLLING_CPLD_STACK_SIZE

| #define POLLING_CPLD_STACK_SIZE 2048 |

◆ POWER_AND_RESET_BUTTON_REG

| #define POWER_AND_RESET_BUTTON_REG 0x00 |

◆ PWRGD_LDO_IN_1V2_R_OFF_REG

| #define PWRGD_LDO_IN_1V2_R_OFF_REG 0x92 |

◆ PWRGD_LDO_IN_1V2_R_ON_REG

| #define PWRGD_LDO_IN_1V2_R_ON_REG 0x4C |

◆ PWRGD_LDO_IN_1V8_R_OFF_REG

| #define PWRGD_LDO_IN_1V8_R_OFF_REG 0x86 |

◆ PWRGD_LDO_IN_1V8_R_ON_REG

| #define PWRGD_LDO_IN_1V8_R_ON_REG 0x58 |

◆ PWRGD_P0V75_AVDD_HSCL_R_OFF_REG

| #define PWRGD_P0V75_AVDD_HSCL_R_OFF_REG 0x89 |

◆ PWRGD_P0V75_AVDD_HSCL_R_ON_REG

| #define PWRGD_P0V75_AVDD_HSCL_R_ON_REG 0x56 |

◆ PWRGD_P0V75_MAX_PHY_N_OFF_REG

| #define PWRGD_P0V75_MAX_PHY_N_OFF_REG 0x8D |

◆ PWRGD_P0V75_MAX_PHY_N_ON_REG

| #define PWRGD_P0V75_MAX_PHY_N_ON_REG 0x4F |

◆ PWRGD_P0V75_MAX_PHY_S_OFF_REG

| #define PWRGD_P0V75_MAX_PHY_S_OFF_REG 0x8F |

◆ PWRGD_P0V75_MAX_PHY_S_ON_REG

| #define PWRGD_P0V75_MAX_PHY_S_ON_REG 0x51 |

◆ PWRGD_P0V75_PVDD_CH_N_OFF_REG

| #define PWRGD_P0V75_PVDD_CH_N_OFF_REG 0x8C |

◆ PWRGD_P0V75_PVDD_CH_N_ON_REG

| #define PWRGD_P0V75_PVDD_CH_N_ON_REG 0x4E |

◆ PWRGD_P0V75_PVDD_CH_S_OFF_REG

| #define PWRGD_P0V75_PVDD_CH_S_OFF_REG 0x8E |

◆ PWRGD_P0V75_PVDD_CH_S_ON_REG

| #define PWRGD_P0V75_PVDD_CH_S_ON_REG 0x50 |

◆ PWRGD_P0V75_TRVDD_ZONEA_R_OFF_REG

| #define PWRGD_P0V75_TRVDD_ZONEA_R_OFF_REG 0x87 |

◆ PWRGD_P0V75_TRVDD_ZONEA_R_ON_REG

| #define PWRGD_P0V75_TRVDD_ZONEA_R_ON_REG 0x54 |

◆ PWRGD_P0V75_TRVDD_ZONEB_R_OFF_REG

| #define PWRGD_P0V75_TRVDD_ZONEB_R_OFF_REG 0x88 |

◆ PWRGD_P0V75_TRVDD_ZONEB_R_ON_REG

| #define PWRGD_P0V75_TRVDD_ZONEB_R_ON_REG 0x55 |

◆ PWRGD_P0V75_VDDC_CLKOBS_R_OFF_REG

| #define PWRGD_P0V75_VDDC_CLKOBS_R_OFF_REG 0x8A |

◆ PWRGD_P0V75_VDDC_CLKOBS_R_ON_REG

| #define PWRGD_P0V75_VDDC_CLKOBS_R_ON_REG 0x57 |

◆ PWRGD_P0V75_VDDPHY_HBM0_HBM2_HBM4_R_OFF_REG

| #define PWRGD_P0V75_VDDPHY_HBM0_HBM2_HBM4_R_OFF_REG 0x90 |

◆ PWRGD_P0V75_VDDPHY_HBM0_HBM2_HBM4_R_ON_REG

| #define PWRGD_P0V75_VDDPHY_HBM0_HBM2_HBM4_R_ON_REG 0x52 |

◆ PWRGD_P0V75_VDDPHY_HBM1_HBM3_HBM5_R_OFF_REG

| #define PWRGD_P0V75_VDDPHY_HBM1_HBM3_HBM5_R_OFF_REG 0x91 |

◆ PWRGD_P0V75_VDDPHY_HBM1_HBM3_HBM5_R_ON_REG

| #define PWRGD_P0V75_VDDPHY_HBM1_HBM3_HBM5_R_ON_REG 0x53 |

◆ PWRGD_P0V85_PVDD_OFF_REG

| #define PWRGD_P0V85_PVDD_OFF_REG 0x8B |

◆ PWRGD_P0V85_PVDD_ON_REG

| #define PWRGD_P0V85_PVDD_ON_REG 0x4D |

◆ PWRGD_P0V9_TRVDD_ZONEA_R_OFF_REG

| #define PWRGD_P0V9_TRVDD_ZONEA_R_OFF_REG 0x77 |

◆ PWRGD_P0V9_TRVDD_ZONEA_R_ON_REG

| #define PWRGD_P0V9_TRVDD_ZONEA_R_ON_REG 0x68 |

◆ PWRGD_P0V9_TRVDD_ZONEB_R_OFF_REG

| #define PWRGD_P0V9_TRVDD_ZONEB_R_OFF_REG 0x78 |

◆ PWRGD_P0V9_TRVDD_ZONEB_R_ON_REG

| #define PWRGD_P0V9_TRVDD_ZONEB_R_ON_REG 0x69 |

◆ PWRGD_P1V1_VDDC_HBM0_HBM2_HBM4_R_OFF_REG

| #define PWRGD_P1V1_VDDC_HBM0_HBM2_HBM4_R_OFF_REG 0x7D |

◆ PWRGD_P1V1_VDDC_HBM0_HBM2_HBM4_R_ON_REG

| #define PWRGD_P1V1_VDDC_HBM0_HBM2_HBM4_R_ON_REG 0x60 |

◆ PWRGD_P1V1_VDDC_HBM1_HBM3_HBM5_R_OFF_REG

| #define PWRGD_P1V1_VDDC_HBM1_HBM3_HBM5_R_OFF_REG 0x7E |

◆ PWRGD_P1V1_VDDC_HBM1_HBM3_HBM5_R_ON_REG

| #define PWRGD_P1V1_VDDC_HBM1_HBM3_HBM5_R_ON_REG 0x61 |

◆ PWRGD_P3V3_OFF_REG

| #define PWRGD_P3V3_OFF_REG 0x93 |

◆ PWRGD_P3V3_ON_REG

| #define PWRGD_P3V3_ON_REG 0x4B |

◆ PWRGD_P3V3_OSC_OFF_REG

| #define PWRGD_P3V3_OSC_OFF_REG 0x94 |

◆ PWRGD_P3V3_OSC_ON_REG

| #define PWRGD_P3V3_OSC_ON_REG 0x4A |

◆ PWRGD_P5V_R_OFF_REG

| #define PWRGD_P5V_R_OFF_REG 0x95 |

◆ PWRGD_P5V_R_ON_REG

| #define PWRGD_P5V_R_ON_REG 0x49 |

◆ PWRGD_PLL_VDDA15_HBM0_HBM2_HBM4_OFF_REG

| #define PWRGD_PLL_VDDA15_HBM0_HBM2_HBM4_OFF_REG 0x84 |

◆ PWRGD_PLL_VDDA15_HBM0_HBM2_HBM4_ON_REG

| #define PWRGD_PLL_VDDA15_HBM0_HBM2_HBM4_ON_REG 0x5C |

◆ PWRGD_PLL_VDDA15_HBM1_HBM3_HBM5_OFF_REG

| #define PWRGD_PLL_VDDA15_HBM1_HBM3_HBM5_OFF_REG 0x85 |

◆ PWRGD_PLL_VDDA15_HBM1_HBM3_HBM5_ON_REG

| #define PWRGD_PLL_VDDA15_HBM1_HBM3_HBM5_ON_REG 0x5D |

◆ PWRGD_PLL_VDDA15_MAX_CORE_N_OFF_REG

| #define PWRGD_PLL_VDDA15_MAX_CORE_N_OFF_REG 0x81 |

◆ PWRGD_PLL_VDDA15_MAX_CORE_N_ON_REG

| #define PWRGD_PLL_VDDA15_MAX_CORE_N_ON_REG 0x59 |

◆ PWRGD_PLL_VDDA15_MAX_CORE_S_OFF_REG

| #define PWRGD_PLL_VDDA15_MAX_CORE_S_OFF_REG 0x82 |

◆ PWRGD_PLL_VDDA15_MAX_CORE_S_ON_REG

| #define PWRGD_PLL_VDDA15_MAX_CORE_S_ON_REG 0x5A |

◆ PWRGD_PLL_VDDA15_PCIE_MAX_CORE_OFF_REG

| #define PWRGD_PLL_VDDA15_PCIE_MAX_CORE_OFF_REG 0x83 |

◆ PWRGD_PLL_VDDA15_PCIE_MAX_CORE_ON_REG

| #define PWRGD_PLL_VDDA15_PCIE_MAX_CORE_ON_REG 0x5B |

◆ PWRGD_PVDD0P9_N_OFF_REG

| #define PWRGD_PVDD0P9_N_OFF_REG 0x79 |

◆ PWRGD_PVDD0P9_N_ON_REG

| #define PWRGD_PVDD0P9_N_ON_REG 0x6A |

◆ PWRGD_PVDD0P9_S_OFF_REG

| #define PWRGD_PVDD0P9_S_OFF_REG 0x7A |

◆ PWRGD_PVDD0P9_S_ON_REG

| #define PWRGD_PVDD0P9_S_ON_REG 0x6B |

◆ PWRGD_PVDD1P5_N_OFF_REG

| #define PWRGD_PVDD1P5_N_OFF_REG 0x71 |

◆ PWRGD_PVDD1P5_N_ON_REG

| #define PWRGD_PVDD1P5_N_ON_REG 0x6C |

◆ PWRGD_PVDD1P5_S_OFF_REG

| #define PWRGD_PVDD1P5_S_OFF_REG 0x72 |

◆ PWRGD_PVDD1P5_S_ON_REG

| #define PWRGD_PVDD1P5_S_ON_REG 0x6D |

◆ PWRGD_VDDA_PCIE_R_OFF_REG

| #define PWRGD_VDDA_PCIE_R_OFF_REG 0x76 |

◆ PWRGD_VDDA_PCIE_R_ON_REG

| #define PWRGD_VDDA_PCIE_R_ON_REG 0x67 |

◆ PWRGD_VDDHTX_PCIE_R_OFF_REG

| #define PWRGD_VDDHTX_PCIE_R_OFF_REG 0x70 |

◆ PWRGD_VDDHTX_PCIE_R_ON_REG

| #define PWRGD_VDDHTX_PCIE_R_ON_REG 0x6E |

◆ PWRGD_VDDQL_HBM0_HBM2_HBM4_R_OFF_REG

| #define PWRGD_VDDQL_HBM0_HBM2_HBM4_R_OFF_REG 0x7B |

◆ PWRGD_VDDQL_HBM0_HBM2_HBM4_R_ON_REG

| #define PWRGD_VDDQL_HBM0_HBM2_HBM4_R_ON_REG 0x62 |

◆ PWRGD_VDDQL_HBM1_HBM3_HBM5_R_OFF_REG

| #define PWRGD_VDDQL_HBM1_HBM3_HBM5_R_OFF_REG 0x7C |

◆ PWRGD_VDDQL_HBM1_HBM3_HBM5_R_ON_REG

| #define PWRGD_VDDQL_HBM1_HBM3_HBM5_R_ON_REG 0x63 |

◆ PWRGD_VPP_HBM0_HBM2_HBM4_R_OFF_REG

| #define PWRGD_VPP_HBM0_HBM2_HBM4_R_OFF_REG 0x7F |

◆ PWRGD_VPP_HBM0_HBM2_HBM4_R_ON_REG

| #define PWRGD_VPP_HBM0_HBM2_HBM4_R_ON_REG 0x5E |

◆ PWRGD_VPP_HBM1_HBM3_HBM5_R_OFF_REG

| #define PWRGD_VPP_HBM1_HBM3_HBM5_R_OFF_REG 0x80 |

◆ PWRGD_VPP_HBM1_HBM3_HBM5_R_ON_REG

| #define PWRGD_VPP_HBM1_HBM3_HBM5_R_ON_REG 0x5F |

◆ RESET_PIN_TO_ICS_STATUS_REG

| #define RESET_PIN_TO_ICS_STATUS_REG 0x2F |

◆ RST_ATH_PWR_ON_PLD_N_ON_REG

| #define RST_ATH_PWR_ON_PLD_N_ON_REG 0x6F |

◆ RSVD_1_REG

| #define RSVD_1_REG 0x0C |

◆ RSVD_2_REG

| #define RSVD_2_REG 0x12 |

◆ RSVD_3_REG

| #define RSVD_3_REG 0x13 |

◆ RSVD_4_REG

| #define RSVD_4_REG 0x26 |

◆ RSVD_GPIO_STATUS_REG

| #define RSVD_GPIO_STATUS_REG 0x32 |

◆ S_OWL_BOOT_SOURCE_REG

| #define S_OWL_BOOT_SOURCE_REG 0x22 |

◆ SYSTEM_ALERT_FAULT_2_REG

| #define SYSTEM_ALERT_FAULT_2_REG 0x99 |

◆ SYSTEM_ALERT_FAULT_REG

| #define SYSTEM_ALERT_FAULT_REG 0x28 |

◆ TEMPERATURE_IC_OVERT_FAULT_2_REG

| #define TEMPERATURE_IC_OVERT_FAULT_2_REG 0x97 |

◆ TEMPERATURE_IC_OVERT_FAULT_REG

| #define TEMPERATURE_IC_OVERT_FAULT_REG 0x2B |

◆ UART_IC_STATUS_REG

| #define UART_IC_STATUS_REG 0x33 |

◆ UBC_MODULE_OC_WARNING_REG

| #define UBC_MODULE_OC_WARNING_REG 0x34 |

◆ VR_AND_CLK_ENABLE_PIN_READING_REG

| #define VR_AND_CLK_ENABLE_PIN_READING_REG 0x01 |

◆ VR_ENABLE_PIN_READING_1_REG

| #define VR_ENABLE_PIN_READING_1_REG 0x02 |

◆ VR_ENABLE_PIN_READING_2_REG

| #define VR_ENABLE_PIN_READING_2_REG 0x03 |

◆ VR_ENABLE_PIN_READING_3_REG

| #define VR_ENABLE_PIN_READING_3_REG 0x04 |

◆ VR_ENABLE_PIN_READING_4_REG

| #define VR_ENABLE_PIN_READING_4_REG 0x05 |

◆ VR_HOT_FAULT_1_REG

| #define VR_HOT_FAULT_1_REG 0x29 |

◆ VR_HOT_FAULT_2_REG

| #define VR_HOT_FAULT_2_REG 0x2A |

◆ VR_POWER_FAULT_1_REG

| #define VR_POWER_FAULT_1_REG 0x0D |

◆ VR_POWER_FAULT_2_REG

| #define VR_POWER_FAULT_2_REG 0x0E |

◆ VR_POWER_FAULT_3_REG

| #define VR_POWER_FAULT_3_REG 0x0F |

◆ VR_POWER_FAULT_4_REG

| #define VR_POWER_FAULT_4_REG 0x10 |

◆ VR_POWER_FAULT_5_REG

| #define VR_POWER_FAULT_5_REG 0x11 |

◆ VR_POWER_GOOD_PIN_READING_1_REG

| #define VR_POWER_GOOD_PIN_READING_1_REG 0x07 |

◆ VR_POWER_GOOD_PIN_READING_2_REG

| #define VR_POWER_GOOD_PIN_READING_2_REG 0x08 |

◆ VR_POWER_GOOD_PIN_READING_3_REG

| #define VR_POWER_GOOD_PIN_READING_3_REG 0x09 |

◆ VR_POWER_GOOD_PIN_READING_4_REG

| #define VR_POWER_GOOD_PIN_READING_4_REG 0x0A |

◆ VR_POWER_GOOD_PIN_READING_5_REG

| #define VR_POWER_GOOD_PIN_READING_5_REG 0x0B |

◆ VR_POWER_INPUT_FAULT_1_REG

| #define VR_POWER_INPUT_FAULT_1_REG 0x2C |

◆ VR_POWER_INPUT_FAULT_2_REG

| #define VR_POWER_INPUT_FAULT_2_REG 0x2D |

◆ VR_SMBUS_ALERT_1_REG

| #define VR_SMBUS_ALERT_1_REG 0x24 |

◆ VR_SMBUS_ALERT_2_REG

| #define VR_SMBUS_ALERT_2_REG 0x25 |

◆ VR_SMBUS_ALERT_3_REG

| #define VR_SMBUS_ALERT_3_REG 0x9A |

◆ VR_SMBUS_ALERT_4_REG

| #define VR_SMBUS_ALERT_4_REG 0x9B |

◆ VR_VENDOR_TYPE_REG

| #define VR_VENDOR_TYPE_REG 0x1C |

Typedef Documentation

◆ aegis_cpld_info

| typedef struct _aegis_cpld_info_ aegis_cpld_info |

Function Documentation

◆ cancel_ubc_delayed_timer_handler()

| void cancel_ubc_delayed_timer_handler | ( | void | ) |

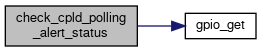

◆ check_cpld_polling_alert_status()

| void check_cpld_polling_alert_status | ( | ) |

Here is the call graph for this function:

◆ check_ubc_delayed()

| void check_ubc_delayed | ( | struct k_work * | work | ) |

◆ check_ubc_delayed_timer_handler()

| void check_ubc_delayed_timer_handler | ( | struct k_timer * | timer | ) |

◆ get_cpld_bit_name()

| const char * get_cpld_bit_name | ( | uint8_t | cpld_offset, |

| uint8_t | bit_pos | ||

| ) |

◆ get_cpld_polling_enable_flag()

| bool get_cpld_polling_enable_flag | ( | void | ) |

◆ get_cpld_reg_name()

| const char * get_cpld_reg_name | ( | uint8_t | cpld_offset | ) |

◆ init_cpld_polling()

| void init_cpld_polling | ( | void | ) |

◆ is_ubc_enabled_delayed_enabled()

| bool is_ubc_enabled_delayed_enabled | ( | void | ) |

◆ plat_set_ac_on_log()

| void plat_set_ac_on_log | ( | ) |

◆ plat_set_dc_on_log()

| void plat_set_dc_on_log | ( | bool | is_assert | ) |

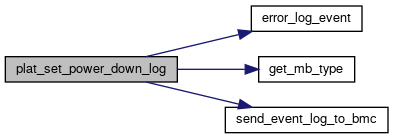

◆ plat_set_power_down_log()

| void plat_set_power_down_log | ( | ) |

Here is the call graph for this function:

◆ set_cpld_polling_enable_flag()

| void set_cpld_polling_enable_flag | ( | bool | status | ) |

◆ set_ubc_enabled_delayed_enabled()

| void set_ubc_enabled_delayed_enabled | ( | bool | status | ) |